DOTTORATO DI RICERCA IN SCIENZE DELL'INGEGNERIA

CICLO XXIX

COORDINATORE Prof. Trillo Stefano

# EMERGING NON VOLATILE MEMORIES RELIABILITY

Settore Scientifico Disciplinare ING/INF-01

**Dottorando** Grossi Alessandro **Tutore** Prof. Olivo Piero

**Correlatore** Dott. Zambelli Cristian

Anni 2014/2016

To Eva, Eleonora, Lorella and Paolo

### Abstract

This work presents the results of the research activity performed during the XXIX-th cycle of the Ph.D. school in Engineering Science of Università degli Studi di Ferrara. In particular the thesis focuses on the electrical characterization, physics, modeling and reliability of innovative non-volatile memories, addressing three of the most promising candidates for the floatinggate based memories replacement which are currently facing a technology dead end. The manuscript is organized as follows.

In Chapter 1 planar CT-NAND memory arrays are considered, showing that the main reliability issues affecting such technology are endurance and retention. Enhanced program and read algorithm able to reduce such limitations will be presented and characterized, highlighting the advantages obtained in terms of reliability. After that, the performances of Solid State Drives (SSD) integrating CT-based memories and using the proposed algorithms will be simulated and evaluated.

In Chapter 2 the results obtained on RRAM will be presented and discussed focusing on the variability, which is the main reliability issue of these nonvolatile memories. The impact of Forming, Set and Reset operations on variability will be evaluated, starting from single pulse operations up to program and verify algorithms. The quantum point contact model will be used to give a physical explanation of the results obtained in characterization. After that, the process parameters impact on variability and reliability will be discussed. Finally, the fundamental variability limits of such technologies will be defined through an extensive array characterization and radiation hard application perspectives will be provided.

In Chapter 3, the results obtained on TAS-MRAM technology will be reported. The reliability and the cell-to-cell variability will be evaluated during endurance tests by extracting a set of characteristic parameters from measurements performed on 1kbits arrays. After a preliminary optimization of the writing parameters on fresh devices, the effectiveness of the optimized parameters will be verified during cycling by evaluating their advantages in terms of cell-to-cell variability and breakdown reduction. After that, a novel TAS-MRAM array with optimized read procedure (Self Referenced) will be tested and compared with the previous one to highlight its advantages in terms of reliability.

The conclusions of this work will be reported at the end of the manuscript outlining what has been accomplished, proposing possible applications for the technologies studied in this thesis and suggesting future works that could extend and improve the understanding of the reliability issues on such memory technologies.

# Contents

| 1        | Intr                                          | oducti                                                         | on                                              | 1                                      |

|----------|-----------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|----------------------------------------|

| <b>2</b> | Cha                                           | urge Tr                                                        | ap NAND                                         | <b>5</b>                               |

|          | 2.1                                           | Basics                                                         |                                                 | 5                                      |

|          | 2.2                                           | Reliab                                                         | ility Issues                                    | 7                                      |

|          |                                               | 2.2.1                                                          | Endurance degradation                           | 8                                      |

|          |                                               | 2.2.2                                                          | Data retention                                  | 9                                      |

|          | 2.3                                           | Enhan                                                          | ced algorithms for reliability improvement      | 11                                     |

|          |                                               | 2.3.1                                                          | Read Retry procedure                            | 12                                     |

|          |                                               | 2.3.2                                                          | Program algorithms                              | 13                                     |

|          | 2.4                                           | Electri                                                        | cal characterization of Charge Trap NAND arrays | 16                                     |

|          | 2.5                                           | SSD a                                                          | pplications perspectives                        | 21                                     |

| 3        | RR.                                           | $\mathbf{A}\mathbf{M}$                                         |                                                 | 27                                     |

|          | 3.1                                           |                                                                |                                                 |                                        |

|          | 0.1                                           | Basics                                                         |                                                 | 28                                     |

|          | 3.2                                           |                                                                | imental Setup                                   | 28<br>32                               |

|          |                                               | Experi                                                         |                                                 |                                        |

|          | 3.2                                           | Experi                                                         | mental Setup                                    | 32                                     |

|          | 3.2                                           | Experi<br>DC an                                                | mental Setup                                    | 32<br>32                               |

|          | 3.2                                           | Experi<br>DC an<br>3.3.1                                       | amental Setup                                   | 32<br>32<br>33                         |

|          | 3.2                                           | Experi<br>DC an<br>3.3.1<br>3.3.2<br>3.3.3                     | Immental Setup                                  | 32<br>32<br>33<br>37                   |

|          | 3.2<br>3.3                                    | Exper:<br>DC an<br>3.3.1<br>3.3.2<br>3.3.3<br>Switch           | amental Setup                                   | 32<br>32<br>33<br>37<br>39<br>45       |

|          | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul> | Exper:<br>DC an<br>3.3.1<br>3.3.2<br>3.3.3<br>Switch           | amental Setup                                   | 32<br>32<br>33<br>37<br>39<br>45       |

|          | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul> | Exper:<br>DC an<br>3.3.1<br>3.3.2<br>3.3.3<br>Switch<br>Increm | amental Setup                                   | 32<br>32<br>33<br>37<br>39<br>45<br>50 |

|    |        | 3.5.3   | Post-Forming modeling                                                        | 60  |

|----|--------|---------|------------------------------------------------------------------------------|-----|

|    |        | 3.5.4   | Endurance analysis                                                           | 64  |

|    |        | 3.5.5   | Forming Oscillations analysis                                                | 68  |

|    | 3.6    | Proces  | s parameters impact on variability                                           | 77  |

|    |        | 3.6.1   | Amorphous vs. Poly-crystalline HfO <sub>2</sub> : array comparison           | 77  |

|    |        | 3.6.2   | $1T-1R$ cells modeling $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 85  |

|    |        | 3.6.3   | Impact of $HfO_2$ process on variability                                     | 93  |

|    | 3.7    | Funda   | mental variability limits in RRAM                                            | 110 |

|    |        | 3.7.1   | Experimental Setup                                                           | 110 |

|    |        | 3.7.2   | Forming for low variability                                                  | 112 |

|    |        | 3.7.3   | Variability in Set/Reset                                                     | 119 |

|    |        | 3.7.4   | Cell to cell VS. cycle to cycle distribution $\ldots \ldots \ldots$          | 119 |

|    |        | 3.7.5   | Variability during cycling                                                   | 124 |

|    | 3.8    | Radiat  | tion hard application perspectives                                           | 128 |

| 4  | TAS    | S-MRA   | AM :                                                                         | 131 |

|    | 4.1    | Basics  |                                                                              | 132 |

|    | 4.2    | Experi  | imental Setup                                                                | 137 |

|    | 4.3    | TAS-N   | ARAM arrays characterization                                                 | 138 |

|    | 4.4    | Self R  | eferenced TAS-MRAM                                                           | 144 |

|    |        | 4.4.1   | Hysteresis analysis                                                          | 147 |

|    |        | 4.4.2   | Endurance                                                                    | 147 |

|    |        | 4.4.3   | Retention                                                                    | 150 |

| 5  | Cor    | nclusio | ns                                                                           | 153 |

| Bi | ibliog | graphy  |                                                                              | 157 |

# List of Figures

| 1.1 | Overview of the actual memory technology scenario 2                                                                                                                                                                                                                                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Emerging memory technologies storage capacity trend in the<br>last years                                                                                                                                                                                                              |

| 2.1 | Examples of Charge Trap (a) and Floating Gate (b) devices $\   6$                                                                                                                                                                                                                     |

| 2.2 | Band diagrams of tunneling mechanisms in planar SONOS CT<br>cell during programming (a) and erase (b). The two different<br>conditions triggering FN or DT are sketched for programming. 7                                                                                            |

| 2.3 | Band diagram sketch of charge transport and trapping/detrappingduring Program (left) and Erase (right) in planar SONOS CTcell.8                                                                                                                                                       |

| 2.4 | Mechanisms involved in the discharging of programmed pla-<br>nar SONOS CT cell: trap-to-band tunneling through the tun-<br>nel layer, Trap-to-band tunneling through the blocking layer,<br>Thermal Emission above the oxide barriers, Thermal emission<br>and subsequent re-trapping |

| 2.5 | Threshold voltage shift induced by fast detrapping (left). Band diagram sketch of fast detrapping effect (right) 10                                                                                                                                                                   |

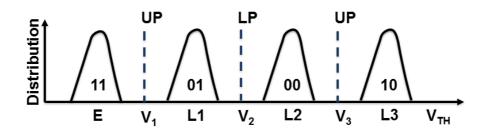

| 2.6 | MLC target distributions and LP, UP discrimination levels $(V_1, V_2, V_3) \dots \dots$                                                                                         |

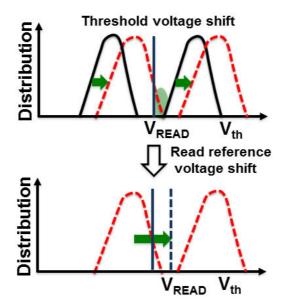

| 2.7  | Read Retry technique schematic: a) Threshold voltage shift<br>induced by increased number of writing operations. Several<br>cells may result in a threshold voltage higher than the reference<br>read voltage $V_{READ}$ , thus producing a read error. b) When<br>the number of erroneous bits is too high to be corrected by<br>ECC the read reference voltage is shifted | 13 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

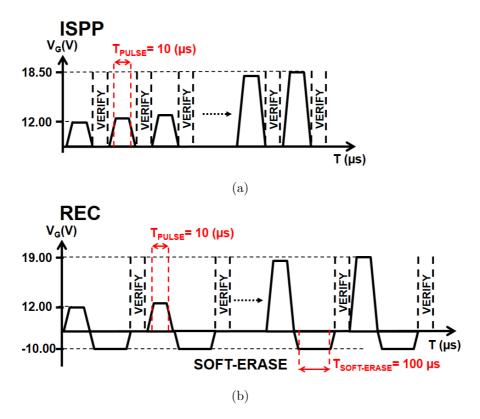

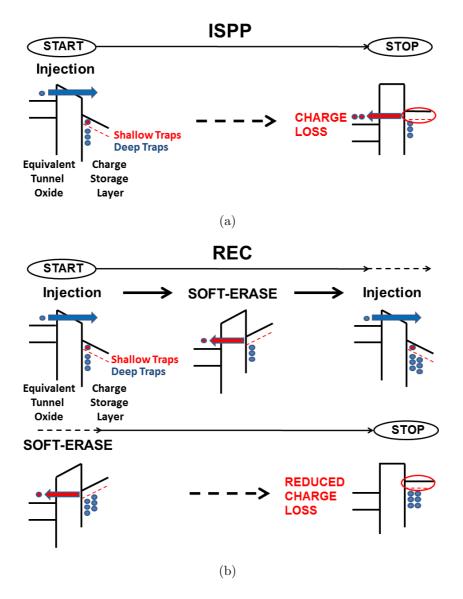

| 2.8  | Schematic of ISPP (a) and REC (b) algorithms                                                                                                                                                                                                                                                                                                                                | 14 |

| 2.9  | Illustration of trapped charge distribution during ISPP (a) and REC (b) program algorithms and charge loss mechanisms                                                                                                                                                                                                                                                       |    |

|      | after writing                                                                                                                                                                                                                                                                                                                                                               | 15 |

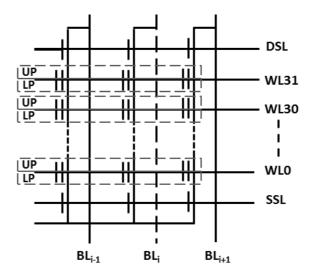

| 2.10 | Schematic representation of the CT cell tested in this work                                                                                                                                                                                                                                                                                                                 | 16 |

| 2.11 | Single block schematic of the 4 Mbits CT-NAND array con-<br>sidered in this work.                                                                                                                                                                                                                                                                                           | 17 |

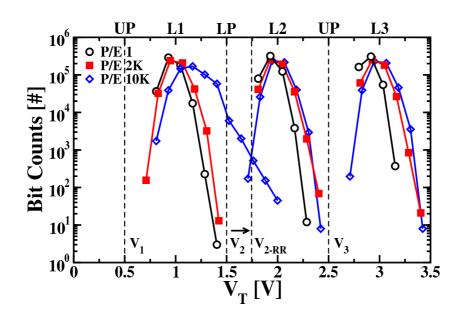

| 2.12 | REC $V_T$ distributions after a Recovery algorithm at P/E=1, 2k, 10k.                                                                                                                                                                                                                                                                                                       | 18 |

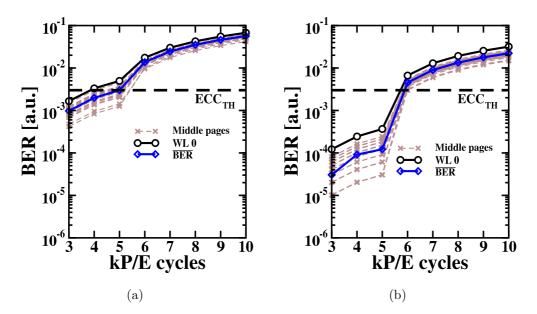

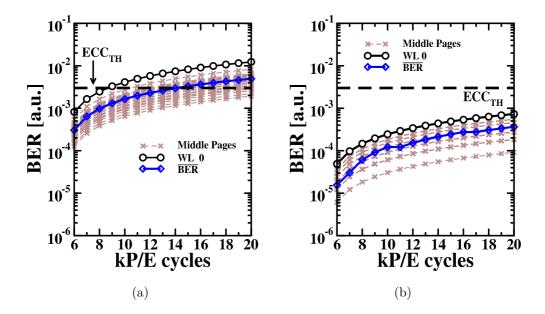

| 2.13 | ISPP programmed cells LP-BER vs. P/E cycle calculated without (a) and with (b) RR procedure, respectively. $ECC_{TH}$ limit corresponding to 100 errors per read page is shown.                                                                                                                                                                                             | 18 |

| 2.14 | REC programmed cells LP-BER vs. P/E cycle calculated<br>without (a) and with (b) RR procedure, respectively. $ECC_{TH}$<br>limit corresponding to 100 errors per read page is shown                                                                                                                                                                                         | 19 |

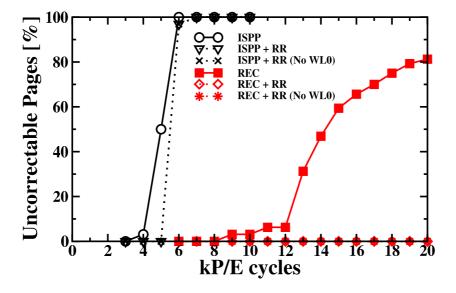

| 2.15 | Uncorrectable pages percentage calculated at different endurance cycles.                                                                                                                                                                                                                                                                                                    | 20 |

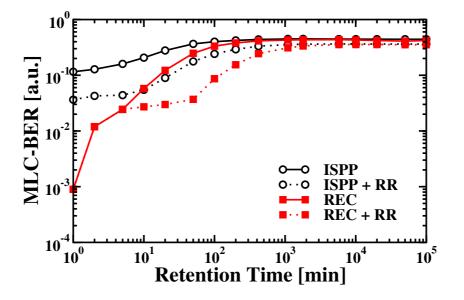

| 2.16 | MLC-BER vs. Retention Time at 85°C after P/E=2k. Dotted<br>and full lines are calculated with and without RR procedure,<br>respectively.                                                                                                                                                                                                                                    | 21 |

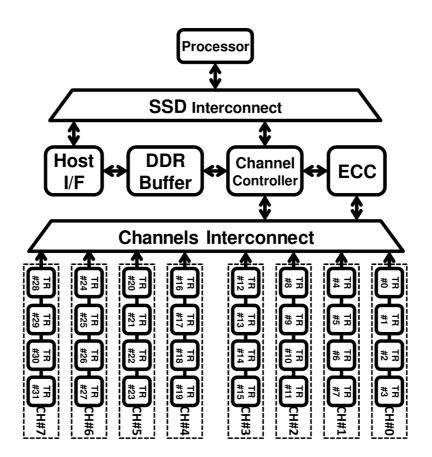

| 2.17 | SSD baseline architecture modeled by the simulator                                                                                                                                                                                                                                                                                                                          | 22 |

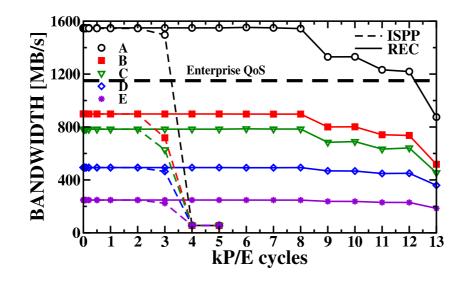

|      | 100 % sequential read throughput calculated at different en-<br>durance cycles with different architecture configurations for                                                                                                                                                                                                                                               |    |

|      | ISPP and REC, respectively                                                                                                                                                                                                                                                                                                                                                  | 24 |

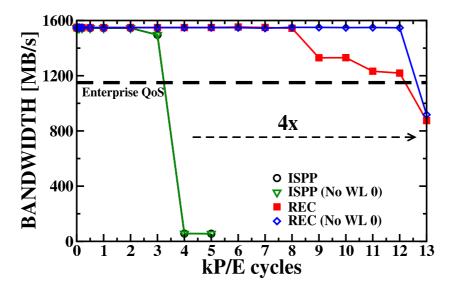

| 2.19 | Sequential read throughput calculated at different endurance cycles.                                                                                                                                                                                                                                                                                                                                   | 24 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

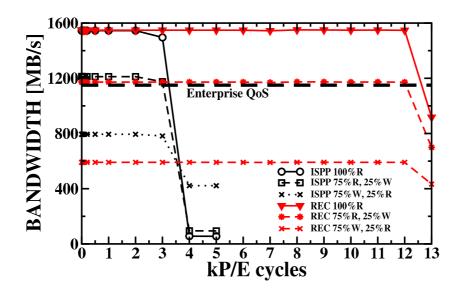

| 2.20 | Random mixed traffic throughput calculated at different en-<br>durance cycles                                                                                                                                                                                                                                                                                                                          | 26 |

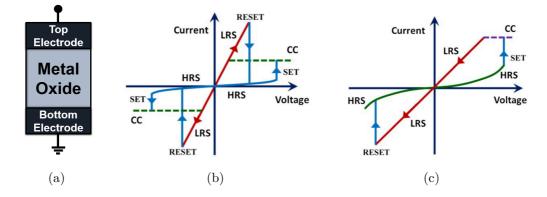

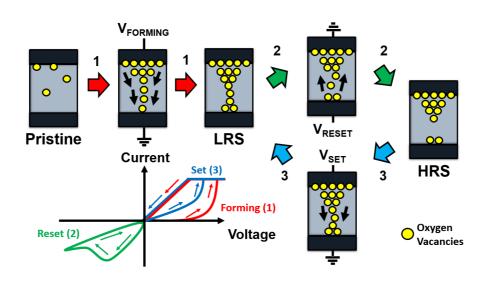

| 3.1  | <ul><li>(a) Schematic of MIM structure for metal oxide RRAM, and</li><li>I-V curves schematic showing two modes of operation: (b)</li><li>Unipolar and (c) Bipolar.</li></ul>                                                                                                                                                                                                                          | 29 |

| 3.2  | Schematic illustration of the switching process in bipolar metal oxide RRAM.                                                                                                                                                                                                                                                                                                                           | 30 |

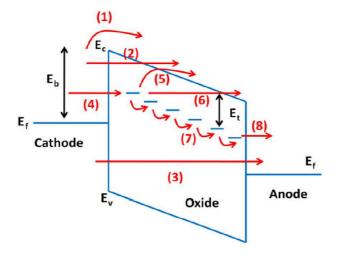

| 3.3  | Schematic of the possible electron conduction paths through<br>a MIM stack.                                                                                                                                                                                                                                                                                                                            | 31 |

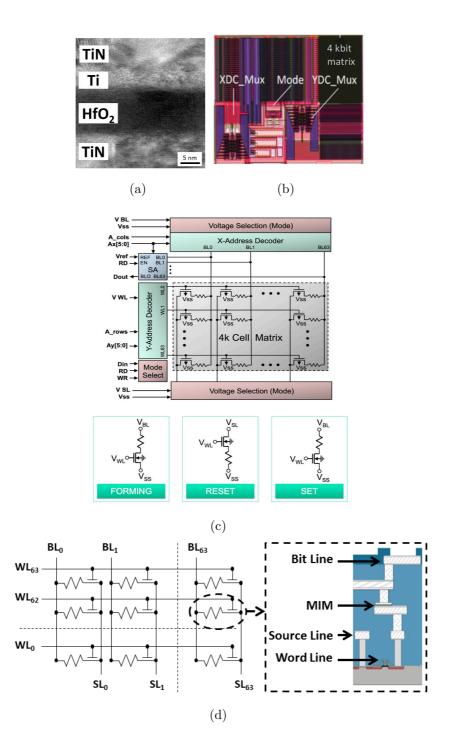

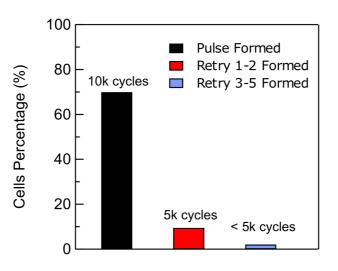

| 3.4  | Cross-Sectional STEM Image of the integrated MIM stack in<br>the RRAM Cell (a). Photograph of the 4 kbit memory array<br>with control circuits (b). Simplified block diagram of the 4<br>kbit memory array (c). Schematic of the 1T-1R cells array<br>and structure of a RRAM cell (d)                                                                                                                 | 34 |

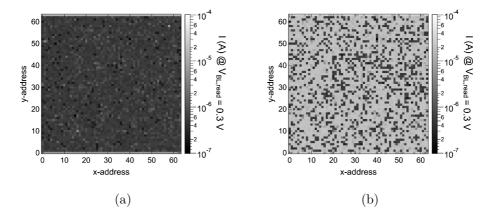

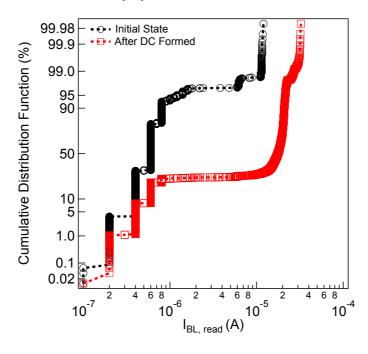

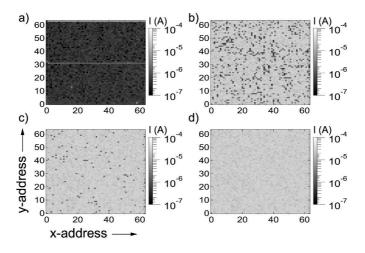

| 3.5  | Current distributions for a 64 $\times$ 64 bit (4 kbit) RRAM array with 1T-1R devices with 600 $\times$ 600 nm <sup>2</sup> MIM area. (a) Initial state. (b) After Forming in DC step sweep. WL voltage in Forming was set to $V_{WL}=1.4V$ with a bitline voltage sweep to $V_{BL}=2.3V$ with ramp rate $dV/dt=0.1~Vs^{-1}.$ Current reading was performed at $V_{WL}=1.4V$ and $V_{BL,read}=0.3V.$ . | 35 |

| 3.6  | Statistical current distributions of the initial state and after<br>Forming in DC sweep. Current reading was performed at $V_{WL}$<br>= 1.4 V and $V_{BL, read} = 0.3 V. \dots \dots \dots \dots \dots$                                                                                                                                                                                                | 36 |

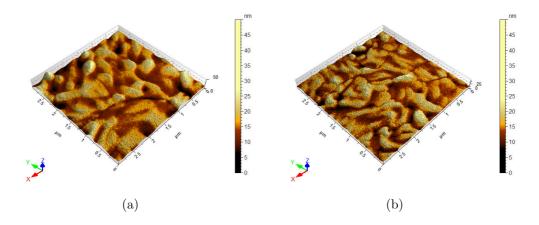

| 3.7  | Roughness profile of the TiN (a) and $HfO_2$ (b) films used in<br>the array processing                                                                                                                                                                                                                                                                                                                 | 37 |

| 3.8  | Current distributions for a $64 \times 64$ bit (4 kbit) RRAM array                            |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | with 1T-1R devices with $600\times600~\mathrm{nm^2}$ MIM area. (a) Initial                    |    |

|      | state. (b) After pulse-induced Forming. $V_{WL}$ was set to 1.4                               |    |

|      | V with $V_{BL} = 3.5$ V and $t_{BL, pulse} = 10 \mu s$ : total 86 % formed.                   |    |

|      | (c) After applying a retry-algorithm to unformed devices: to-                                 |    |

|      | tal 97.6 $\%$ formed. (d) After DC Forming of the devices not                                 |    |

|      | formed by the retry step: total $100\%$ formed. Current reading                               |    |

|      | was performed at $V_{WL} = 1.4V$ and $V_{BL,\ read} = 0.3V.$                                  | 38 |

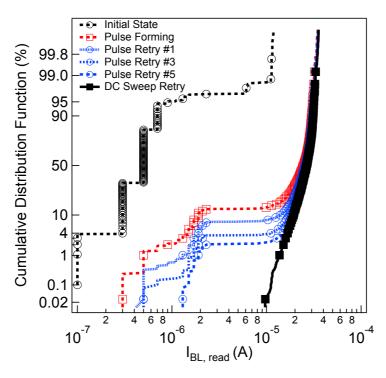

| 3.9  | Statistical current distributions of the initial state, after pulse-                          |    |

|      | induced Forming and after application of retry-algorithms.                                    |    |

|      | Current reading was performed at $V_{\rm WL}=1.4\rm V$ and $V_{\rm BL,\ read}$                |    |

|      | $= 0.3 \mathrm{V}.  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 39 |

| 3.10 | Set/Reset cycling endurance after pulse-induced forming and                                   |    |

|      | after pulse-retry forming                                                                     | 40 |

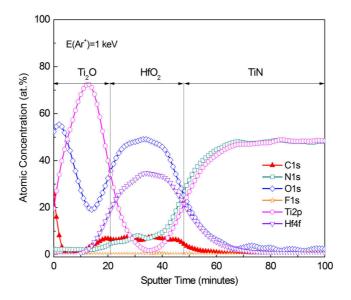

| 3.11 | XPS depth profile measurement of a 50 nm thick $HfO_2 RRAM$                                   |    |

|      |                                                                                               | 41 |

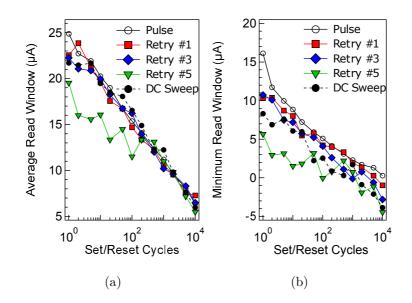

| 3.12 | (a) Average and (b) minimum read window after a single pulse,                                 |    |

|      | after 1, 3, 5 forming-retry pulses and after DC sweep                                         | 42 |

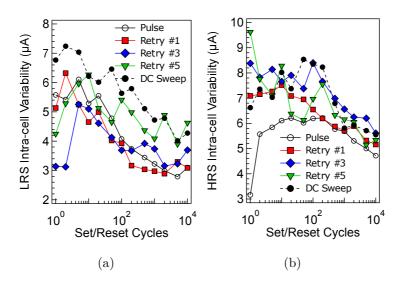

| 3.13 | Intra-cell variability during $10^4$ pulse set/reset cycling for (a)                          |    |

|      | LRS and (b) HRS.                                                                              | 42 |

| 3.14 | HRS I-V curves measured on cycled devices after Reset on cells                                |    |

|      | formed with a single pulse (a) and with DC retry operation (b).                               | 43 |

| 3.15 | Schematic showing the conductive filament shape after Reset                                   |    |

|      | (HRS) for Pulse and DC Retry formed cells                                                     | 44 |

| 3.16 | Cumulative distribution of conductance values measured after                                  |    |

|      | Reset on cycled cells                                                                         | 45 |

| 3.17 | Set (a) and Reset (b) switching kinetics performed on 30 cells                                |    |

|      | in the RRAM array test structure                                                              | 46 |

| 3.18 | Cumulative distribution of the Set and Reset switching volt-                                  |    |

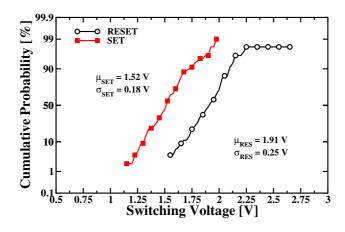

|      |                                                                                               | 47 |

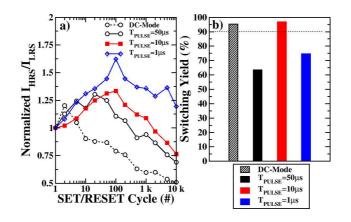

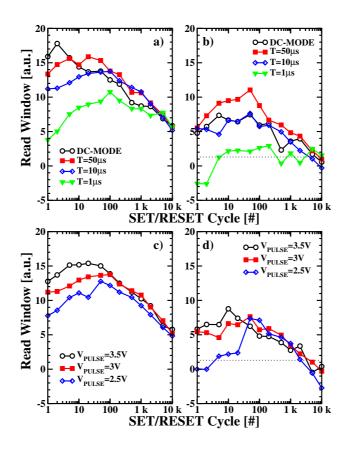

| 3.19 | Normalized read current Ratio (a) and Switching Yield (b)<br>evaluation for different Set/Reset modes (DC and pulses with |    |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

|      | different durations) during cycling. $V_{pulse} = 3 V$ for pulsed                                                         |    |

|      | modes                                                                                                                     | 48 |

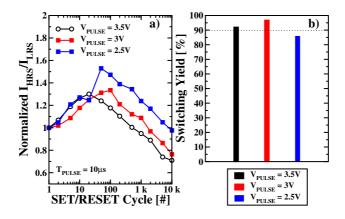

| 3.20 | Normalized read current Ratio (a) and Switching Yield (b) for                                                             |    |

|      | different Set/Reset pulse amplitudes during cycling. $\mathbf{T}_{pulse} =$                                               |    |

|      | 10 $\mu$ s                                                                                                                | 48 |

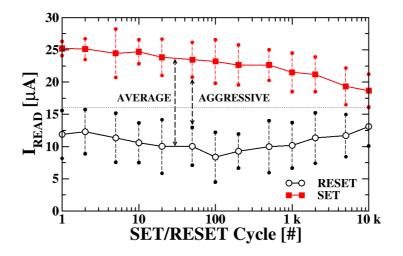

| 3.21 | Set and Reset read current behavior during cycling with $V_{pulse}$                                                       |    |

|      | = 3 V, $T_{pulse} = 10 \ \mu s$ . Average and aggressive read window                                                      |    |

|      | calculation points are indicated                                                                                          | 49 |

| 3.22 | Read Window trends in cycling. Average (left column) and                                                                  |    |

|      | aggressive (right column) measurements: a) and b) same con-                                                               |    |

|      | ditions as Fig. 3.19; c) and d) same conditions as in Fig. 3.20.                                                          |    |

|      | The limit for the Set/Reset discrimination is depicted at read                                                            |    |

|      | window = $3 \mu A$                                                                                                        | 50 |

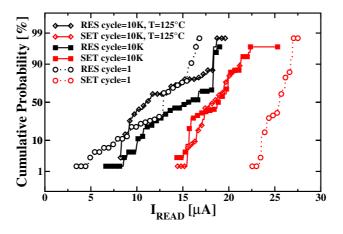

| 3.23 | Read current cumulative distributions at Set/Reset cycle $1$                                                              |    |

|      | and 10K for a pulsed Set/Reset $V_{pulse} = 3$ V, $T_{pulse} = 10 \ \mu s$                                                |    |

|      | and temperature bake effect                                                                                               | 51 |

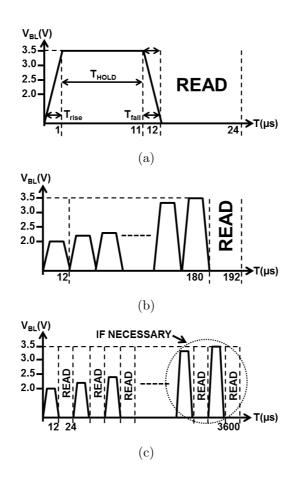

| 3.24 | Single Pulse (a), $IF$ (b) and $IFV$ (c) Forming schemes                                                                  | 54 |

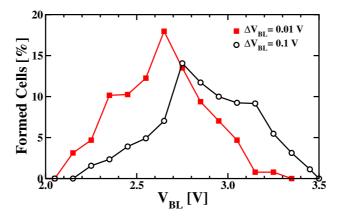

| 3.25 | Distributions of the forming voltages during $IFV$ for the $\Delta V_{BL}$                                                |    |

|      | = 0.01 V and $\Delta V_{BL}$ = 0.1 V cases                                                                                | 54 |

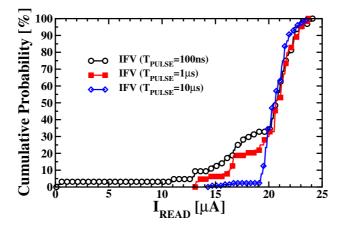

| 3.26 | Cumulative $I_{read}$ distributions after IFV with $\Delta V_{BL} = 0.01$ V                                               |    |

|      | and different pulse widths                                                                                                | 55 |

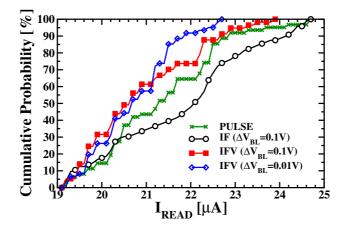

| 3.27 | Cumulative $I_{read}$ distributions of correctly formed cells after                                                       |    |

|      | Pulse (54%), IF (77%), IFV with $\Delta V_{BL} = 0.1$ V (87%) and                                                         |    |

|      | IFV with $\Delta V_{BL} = 0.01$ V (99%) forming operations                                                                | 57 |

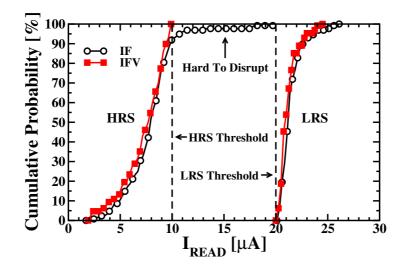

| 3.28 | IF and IFV cumulative $I_{HRS}$ and $I_{LRS}$ distributions measured                                                      |    |

|      | at endurance cycle 1                                                                                                      | 58 |

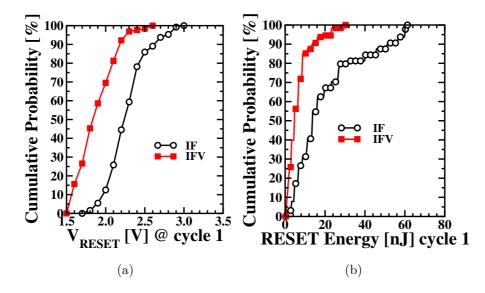

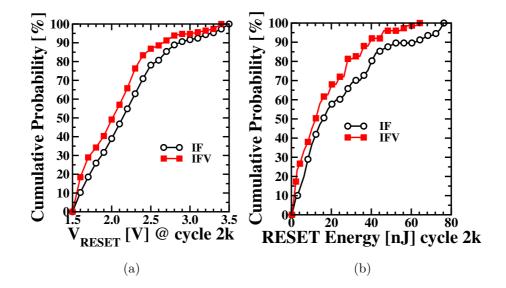

| 3.29 | Cumulative distribution of the reset switching voltages (a) and                                                           |    |

|      | overall Energy required to perform Reset operation (b) at cycle                                                           |    |

|      | 1 for <i>IF</i> and <i>IFV</i> ( $\Delta V_{BL} = 0.01$ V) forming schemes                                                | 59 |

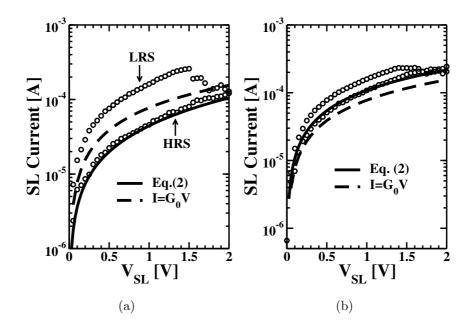

| 3.30 | Reset I-V characteristics measured after forming and HRS fit-<br>ting through eq.(3.2) on correctly working cells (a) and hard<br>to disrupt cells (b)                                                                                                                                       | 61       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.31 | Schematic showing the conductive filament shape after Reset (HRS) for correctly working and hard to disrupt cells                                                                                                                                                                            | 62       |

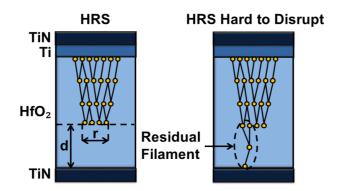

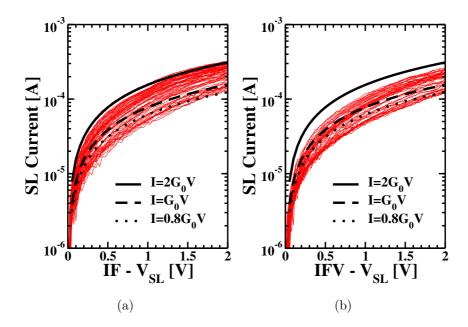

| 3.32 | HRS curves obtained after Reset I-V operation on $IF$ (a) and $IFV$ with $\Delta V_{BL} = 0.01$ V (b) formed cells                                                                                                                                                                           | 62       |

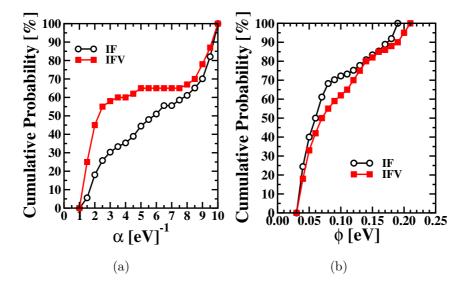

| 3.33 | Cumulative distribution of $\alpha$ and $\Phi$ fitting parameters used on correctly working cells                                                                                                                                                                                            | 63       |

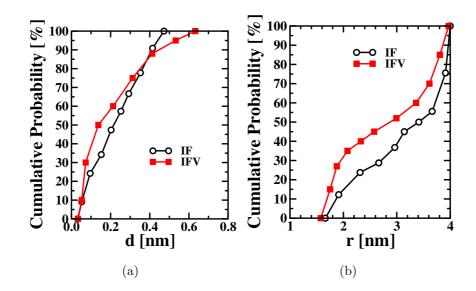

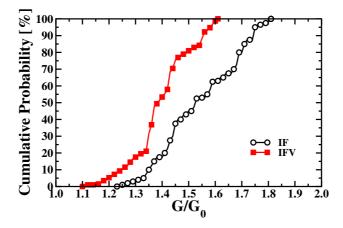

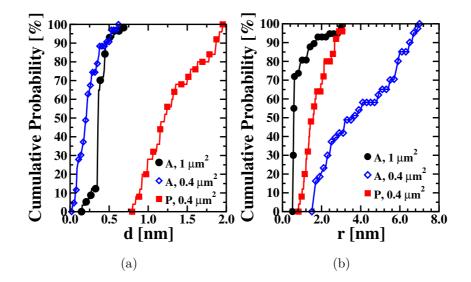

| 3.34 | Cumulative distribution of calculated barrier length $d$ (a) and<br>radius of the filament constriction $r$ (b) on correctly working                                                                                                                                                         | 64       |

| 3.35 | cells                                                                                                                                                                                                                                                                                        | 64<br>64 |

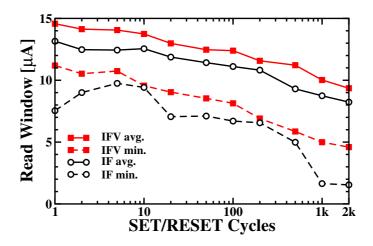

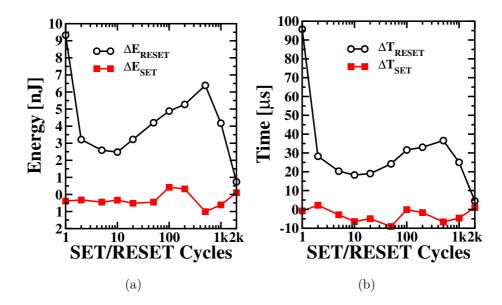

| 3.36 | Average and minimum read windows as a function of the Set/Reset cycle number for <i>IF</i> and <i>IFV</i> ( $\Delta V_{BL} = 0.01$ V) forming schemes.                                                                                                                                       | 65       |

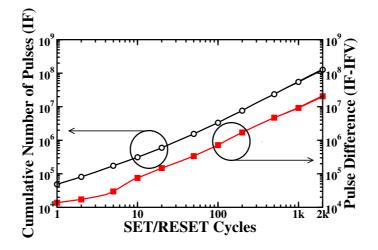

| 3.37 | Cumulative number of Set/Reset pulses applied to the entire<br>memory as a function of the cycle number for the <i>IF</i> forming<br>scheme (left axis) and cumulative pulse number saving for the<br>$IFV (\Delta V_{BL} = 0.01 \text{ V})$ forming scheme with respect to <i>IF</i> (right |          |

| 3.38 | axis)                                                                                                                                                                                                                                                                                        | 66<br>67 |

| 3.39 | Average difference between $IF$ and $IFV$ ( $\Delta V_{BL} = 0.01$ V) Energy (a) and Time (b) required to perform Set and Reset operations as a function of the Set/Reset cycle number                                                                                                       | 67       |

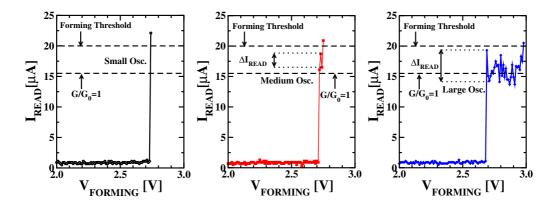

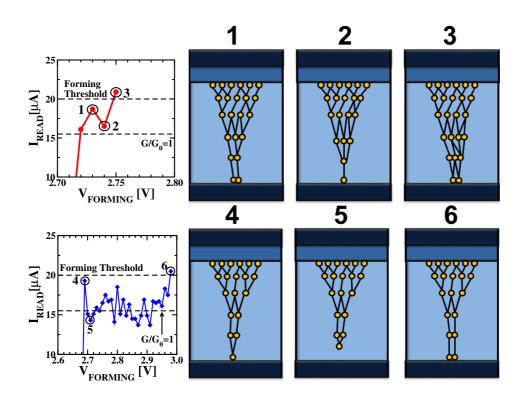

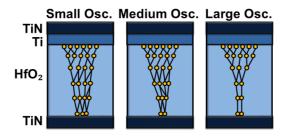

| 3.40 | Three different behaviors observed during forming process:                                                                                      |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | small (left), medium (centre) and large (right) read-verify cur-                                                                                |    |

|      | rent oscillations                                                                                                                               | 69 |

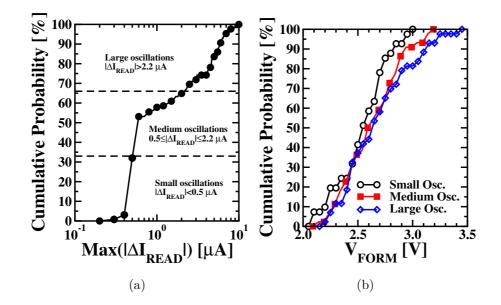

| 3.41 | Cumulative distribution of the maximum read current oscilla-                                                                                    |    |

|      | tions measured during forming (a). Cumulative distribution                                                                                      |    |

|      | of the forming voltage for the three forming oscillations groups                                                                                |    |

|      | (b)                                                                                                                                             | 70 |

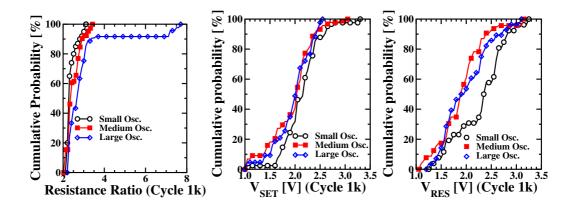

| 3.42 | Resistance ratio, $V_{SET}$ , $V_{RES}$ cumulative distributions for the                                                                        |    |

|      | different forming oscillations groups calculated on cycled devices.                                                                             | 71 |

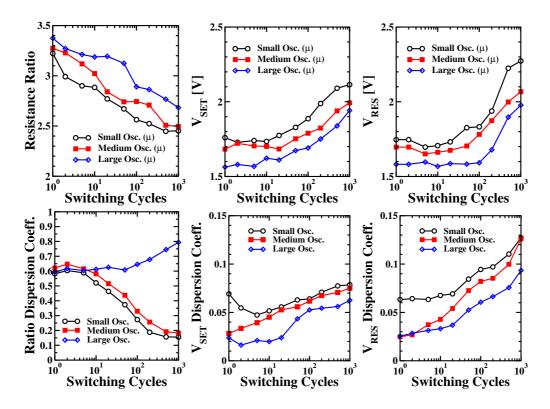

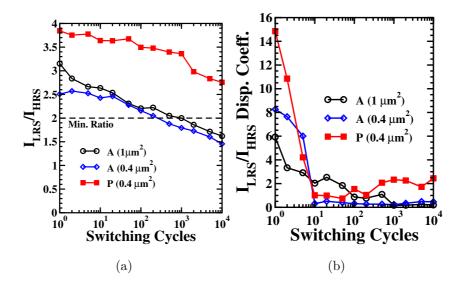

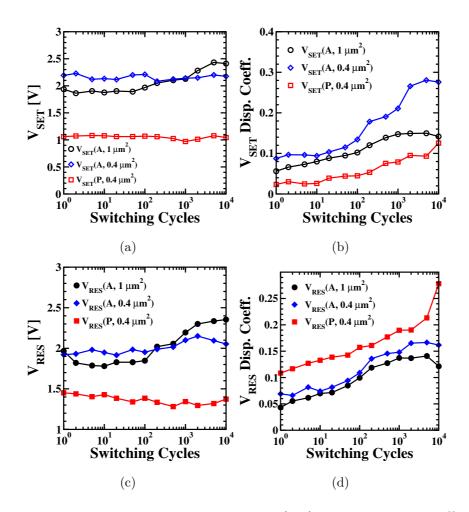

| 3.43 | Resistance Ratio, $V_{SET}$ and $V_{RES}$ average values and disper-                                                                            |    |

|      | sion coefficients calculated during cycling.                                                                                                    | 71 |

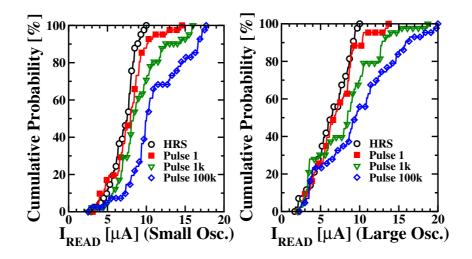

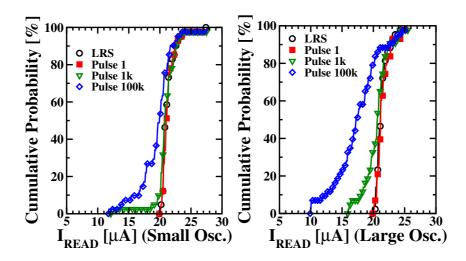

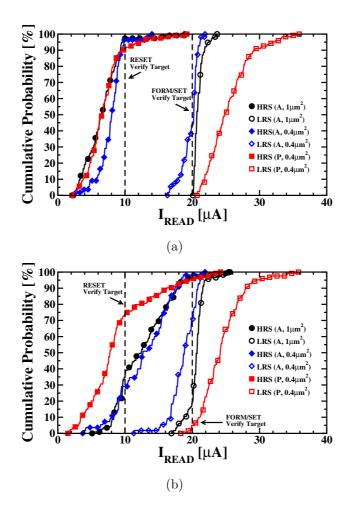

| 3.44 | Cumulative distributions of the read currents (with $V_{read} =$                                                                                |    |

|      | 0.2V) measured during set stress on HRS after different num-                                                                                    |    |

|      | ber of disturb pulses, at endurance cycle 1                                                                                                     | 73 |

| 3.45 | Cumulative distributions of the read currents (with $V_{read} =$                                                                                |    |

|      | 0.2V) measured during reset stress on LRS after different num-                                                                                  |    |

|      | ber of disturb pulses, at endurance cycle 1                                                                                                     | 73 |

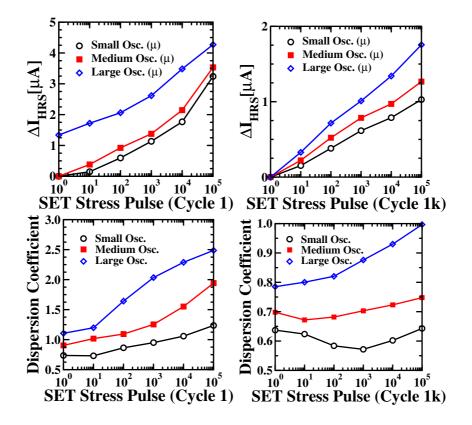

| 3.46 | Average read current variation $(V_{READ} = 0.2V)$ of LRS and                                                                                   |    |

|      | dispersion coefficient evolution calculated during 100k reset                                                                                   |    |

|      | pulse stress, with $V_{pulse} = 0.8V$ after endurance cycle 1 (left)                                                                            |    |

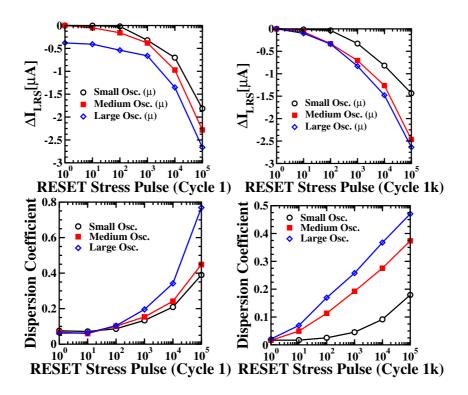

|      | and 1k (right)                                                                                                                                  | 74 |

| 3.47 | Average read current variation $(V_{READ} = 0.2V)$ of HRS and                                                                                   |    |

|      | dispersion coefficient evolution calculated during $100k$ set pulse                                                                             |    |

|      | stress, with $V_{pulse} = 0.8V$ after endurance cycle 1 (left) and 1k                                                                           |    |

|      | $(right). \ldots \ldots$ | 75 |

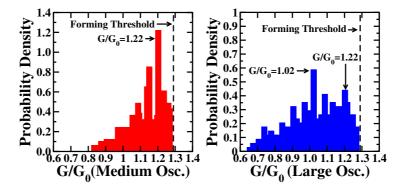

| 3.48 | Distribution of the read-verify current values measured during                                                                                  |    |

|      | forming process in units of $G_0$                                                                                                               | 75 |

| 3.49 | Schematic representation of the CF evolution during medium                                                                                      |    |

|      | (1,2,3) and large $(4,5,6)$ read-verify current oscillations                                                                                    | 76 |

| 3.50 | Schematic representation of the post-forming conductive fila-                                                                                   |    |

|      | ments showing different current oscillation properties                                                                                          | 76 |

| 3.51 | $I_{LRS}/I_{HRS}$ current ratio average values (a) and dispersion co-                                                                                                                                                                                                                                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | efficients (b) calculated during cycling. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                | 80 |

| 3.52 | $I_{HRS}$ and $I_{LRS}$ cumulative distributions at cycle 1 (a) and at cycle 10k (b).                                                                                                                                                                                                                                        | 81 |

| 3.53 | $V_{SET}$ and $V_{RES}$ average values (a,b) and dispersion coeffi-                                                                                                                                                                                                                                                          |    |

|      | cients (c,d) calculated during cycling                                                                                                                                                                                                                                                                                       | 82 |

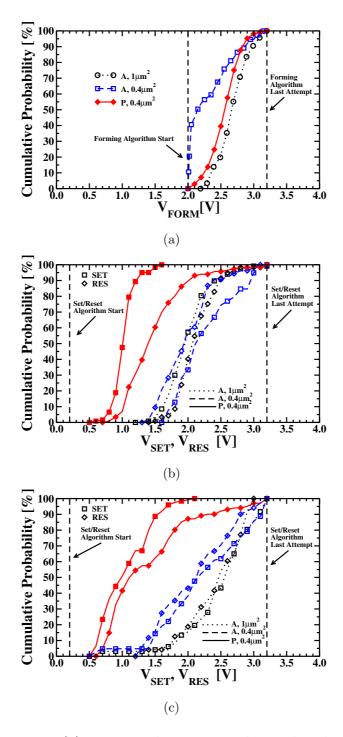

| 3.54 | $V_{FORM}$ (a), $V_{SET}$ and $V_{RES}$ cumulative distributions at cycle 1 (b) and at cycle 10k (c)                                                                                                                                                                                                                         | 83 |

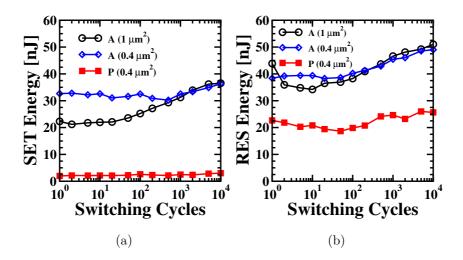

| 3.55 | Energy required to perform Set (a) and Reset (b) operations<br>as a function of the Set/Reset cycle number                                                                                                                                                                                                                   | 84 |

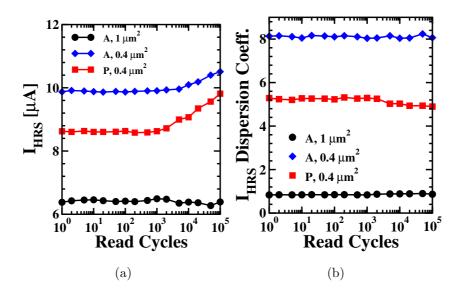

| 3.56 | Average read current variation (a) and dispersion coefficient<br>evolution (b) of HRS calculated during 100k read disturb pulses,<br>with $V_{pulse} = 0.2$ V                                                                                                                                                                | 85 |

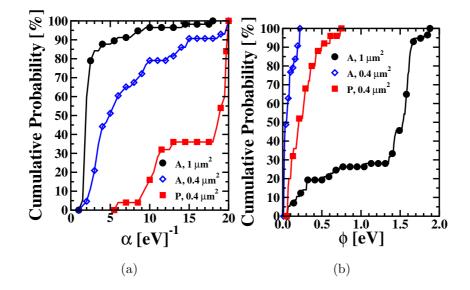

| 3.57 | Cumulative distribution of $\alpha$ and $\Phi$ fitting parameters used on CF break cells.                                                                                                                                                                                                                                    | 87 |

| 3.58 | Cumulative distribution of calculated barrier length $d$ (a) and<br>radius of the filament constriction $r$ (b) on CF break cells                                                                                                                                                                                            |    |

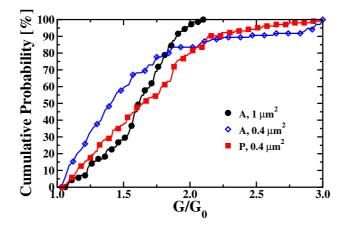

| 3.59 | Cumulative distribution of $G/G_0$ fitting parameters used on<br>hard to disrupt cells.                                                                                                                                                                                                                                      | 89 |

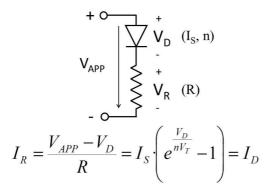

| 3.60 | Equivalent model for the 1T-1R device based on a Diode-<br>Resistor circuit. Resistance (R), saturation current $(I_s)$ and<br>ideality factor (n) of the diode are the parameters used to fit<br>the conduction of the 1T-1R devices at both resistive states,<br>LRS and HRS, and for both types of samples, amorphous and |    |

|      | poly-crystalline                                                                                                                                                                                                                                                                                                             | 90 |

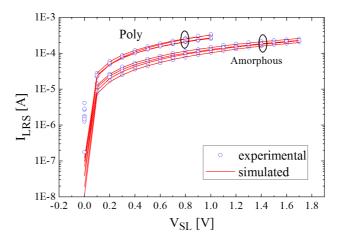

| 3.61 | Experimental LRS I-V curves (circles) and the simulated curves                                                                                                                                                                                                                                                               |    |

|      | (continuous lines) obtained using the Diode-Resistor model.                                                                                                                                                                                                                                                                  |    |

|      | With a suitable parameter Set, the model reproduces properly                                                                                                                                                                                                                                                                 |    |

|      | the experimental curves for both poly-crystalline and amor-                                                                                                                                                                                                                                                                  |    |

|      | phous samples.                                                                                                                                                                                                                                                                                                               | 91 |

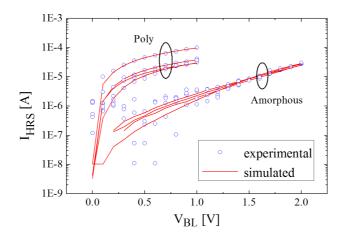

| 3.62 | Experimental HRS I-V curves (circles) and simulated HRS<br>curves (continuous lines) using the Diode-Resistor model for<br>both amorphous and poly-crystalline samples. Noisy currents<br>at low voltages cannot be fitted by the model, especially for<br>the amorphous samples where current values for $V_{BL}$ below 1<br>V are not considered | 2 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

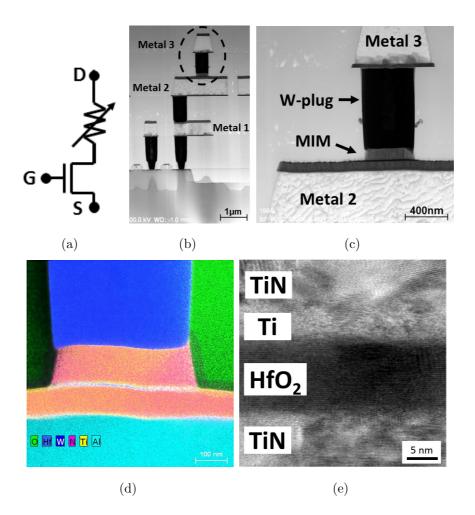

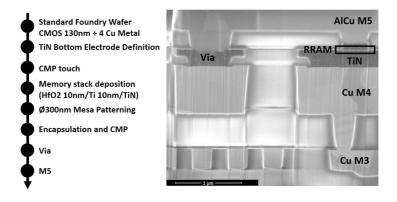

| 3.63 | Schematic (a), cross-sectional TEM image of the 1T-1R cell<br>(b), and MIM stack insight (c). Energy-dispersive X-ray spec-<br>troscopy (EDX) of the MIM stack, tungsten plug, and Metal<br>2 (d), and high magnification TEM image of the MIM (e) 94                                                                                              | 1 |

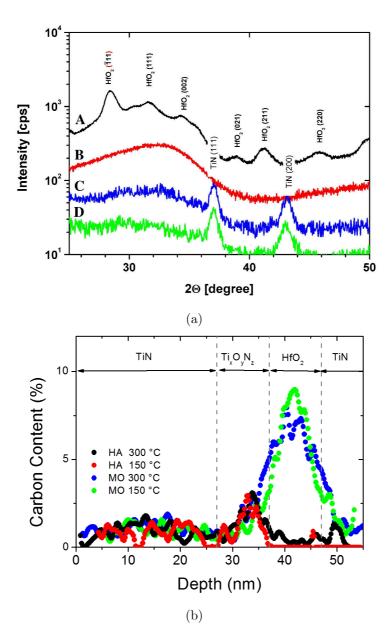

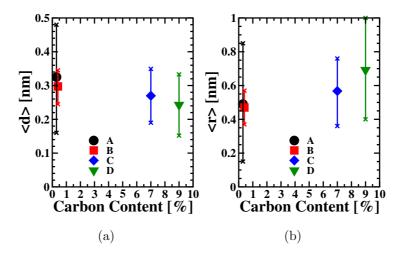

| 3.64 | XRD (a) and XPS (b) analysis on the four considered processes. The XPS reveals the carbon content in the $HfO_2$ 96                                                                                                                                                                                                                                | 3 |

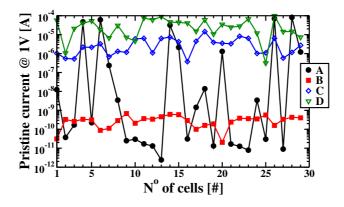

| 3.65 | Pristine current measured at 1 V for the four considered pro-<br>cesses                                                                                                                                                                                                                                                                            | 7 |

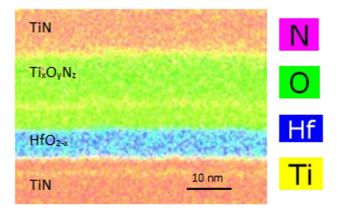

| 3.66 | Mapping of the elements N, O, Hf and Ti by EDX of a process C MIM cell (similar results were obtained on all processes).<br>The nitrogen and oxygen gettering activity at the Ti/HfO <sub>2</sub> interface after annealing at 400°C in forming gas atmosphere is represented by the thick $Ti_x O_y N_z$ layer                                    | 3 |

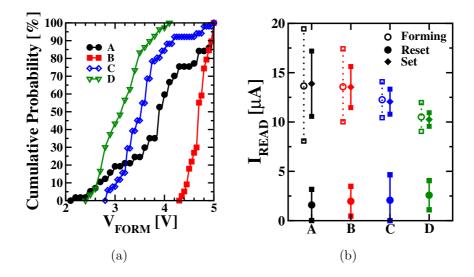

| 3.67 | Cumulative distribution of the Forming voltages measured on<br>processes A, B, C and D (a). Read current average values and<br>standard deviations (in $\mu$ A) after Forming, Set and Reset (b). 99                                                                                                                                               | 9 |

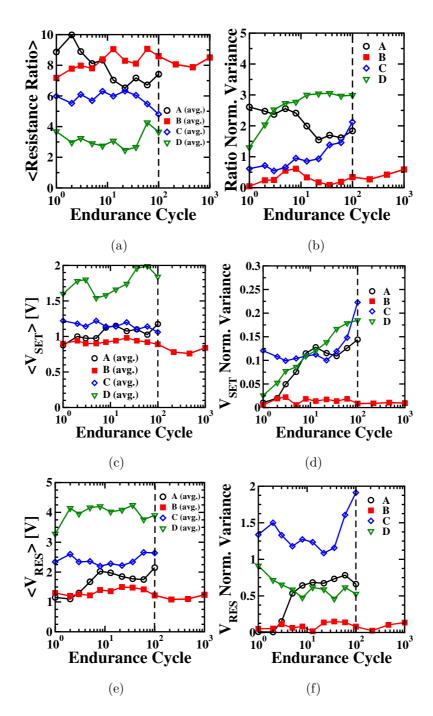

| 3.68 | Resistance Ratio, $V_{SET}$ and $V_{RES}$ average values and normal-<br>ized variances calculated on 20 cells for each process during<br>cycling                                                                                                                                                                                                   | 2 |

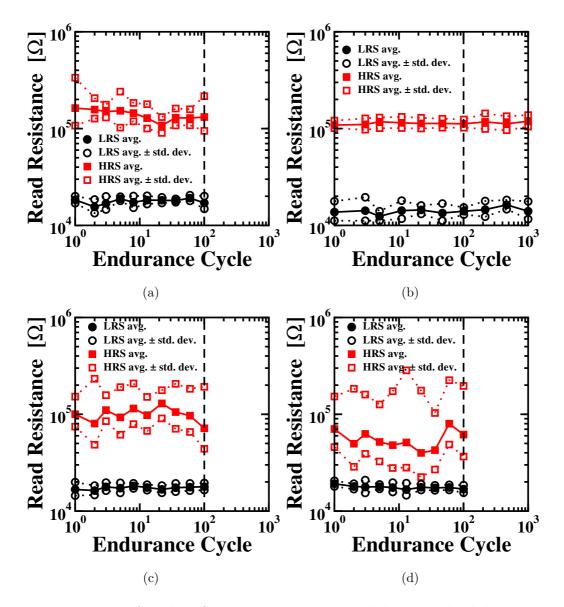

| 3.69 | HRS and LRS average resistances and their standard deviation calculated on 20 cells for each process during cycling 103                                                                                                                                                                                                                            | 3 |

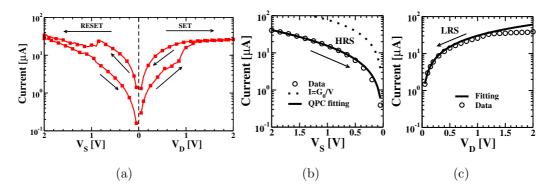

| 3.70 | Typical I-V characteristic measured on a process B random<br>sampled cell (a), HRS fitting (b) and LRS fitting (c) through<br>QPC                                                                                                                                                                                                                  |   |

|      | $\forall r \cup \dots \dots$                                                                                                                                                                                                                       | J |

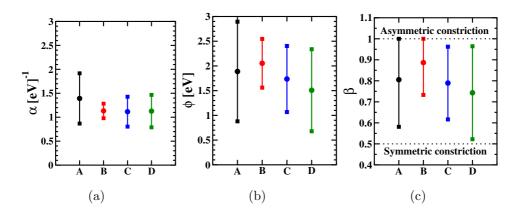

| 3.71 | Distributions of the QPC model fitting parameters $\alpha$ (a), $\phi$                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|      | (b) and $\beta$ (c)                                                                                                                              |

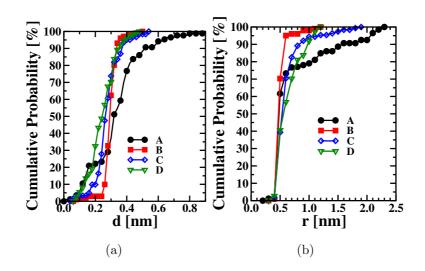

| 3.72 | Cumulative distribution of calculated barrier length $d$ (a) and                                                                                 |

|      | radius of the filament constriction $r$ (b)                                                                                                      |

| 3.73 | Schematic showing the conductive filament shape after Reset. $\ 108$                                                                             |

| 3.74 | Average values of calculated barrier length $d$ (a) and radius of                                                                                |

|      | the filament constriction $r$ (b). Error bars show the standard                                                                                  |

|      | deviation                                                                                                                                        |

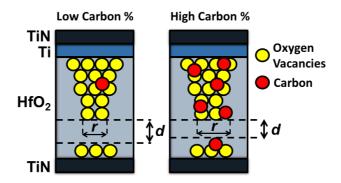

| 3.75 | Schematic showing the effect of carbon on barrier length $d$ and                                                                                 |

|      | conductive filament constriction $r$                                                                                                             |

| 3.76 | Description of the integration flow and TEM cross section of                                                                                     |

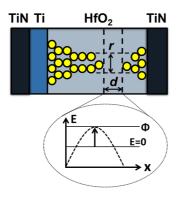

|      | the integrated TiN/HfO <sub>2</sub> /Ti/TiN OxRAM                                                                                                |

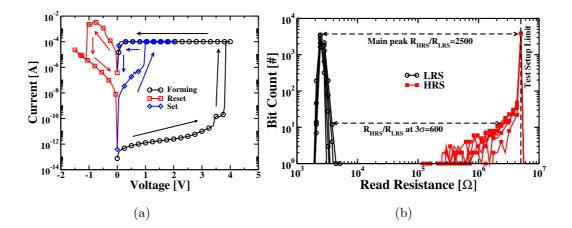

| 3.77 | 1R Forming, Set and Reset I-V curves (a). LRS and HRS                                                                                            |

|      | distributions measured on 4 kbits array with Set and Reset                                                                                       |

|      | conditions allowing to obtain large resistance window (b) 111                                                                                    |

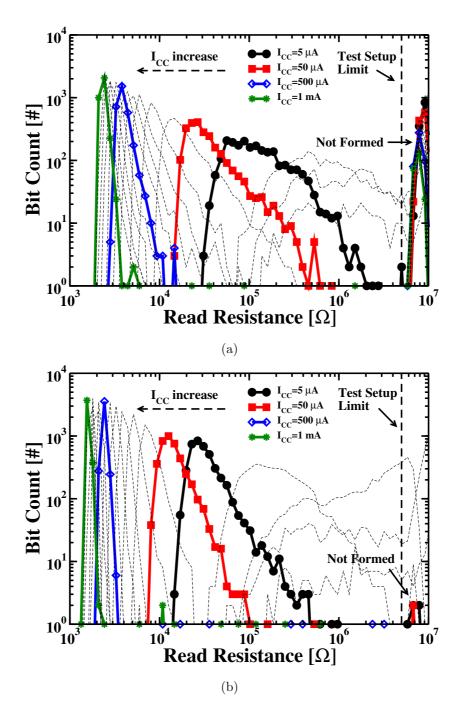

| 3.78 | Forming with increasing $I_{CC}$ and $V_{BL}=4V$ : read resistance                                                                               |

|      | distributions evolution with $T_{PULSE}=100$ ns (a) and $10\mu$ s (b).                                                                           |

|      | Dotted lines show the distribution evolution                                                                                                     |

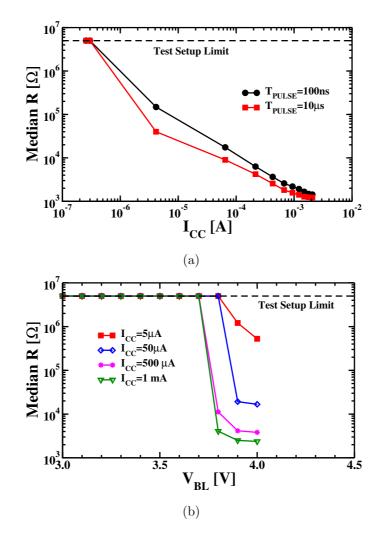

| 3.79 | Median resistance as a function of increasing $I_{CC}$ with $V_{BL}=4V$ ,                                                                        |

|      | $T_{PULSE}=100$ ns and $10\mu$ s (a). Forming with $V_{BL}$ increasing,                                                                          |

|      | $T_{PULSE}$ =100ns and different $I_{CC}$ (b)                                                                                                    |

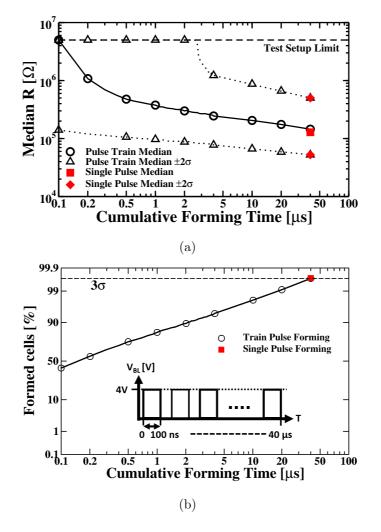

| 3.80 | Median resistance $\pm 2\sigma$ during pulse train Forming procedure                                                                             |

|      | with $I_{CC}=5\mu A$ , $V_{BL}=4V$ , $T_{PULSE}=100$ ns and after Forming                                                                        |

|      | with a single pulse of the same cumulative time $T_{PULSE} = 40 \mu s$                                                                           |

|      | (a). Formed cells percentage during pulse train Forming and                                                                                      |

|      | after single pulse Forming (b)                                                                                                                   |

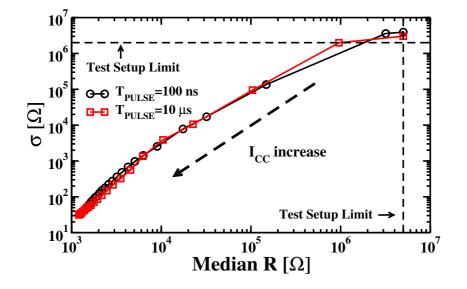

| 3.81 | Median resistance and $\sigma$ evolution during Forming with in-                                                                                 |

|      | creasing $I_{CC}$ , $V_{BL}$ = 4 V, $T_{PULSE}$ = 100 ns and 10 $\mu$ s 116                                                                      |

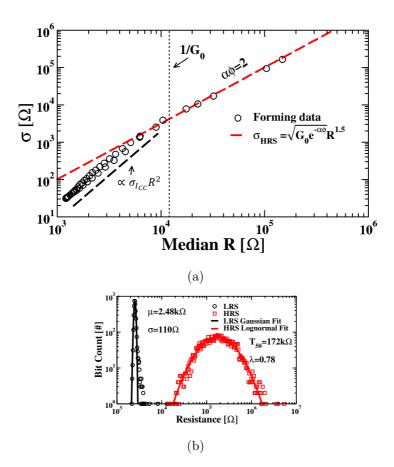

| 3.82 | $\sigma$ vs. median R fit above 1/G_0 (a). LRS and HRS distribu-                                                                                 |

|      | tions fitting after Forming with $I_{CC}=5 \ \mu A$ , $V_{BL}=4 \ V$ and                                                                         |

|      | $T_{PULSE} = 40 \ \mu s \ (b) \dots \dots$ |

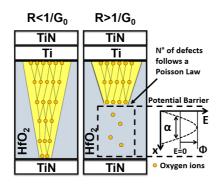

| 3.83 | CF schematic representation in case of R below and above                         |

|------|----------------------------------------------------------------------------------|

|      | $1/{\rm G}_0.$ QPC model parameters $\alpha$ and $\phi$ are depicted. $~$ 117    |

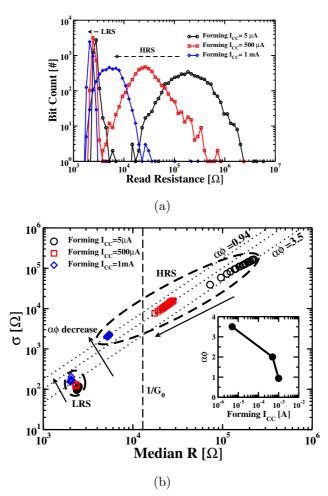

| 3.84 | LRS and HRS distributions after Forming with $V_{BL}=4V$ , $T_{PULSE}$           |

|      | allowing to form up to $3\sigma$ cells and different $I_{CC}$ (a). LRS and       |

|      | HRS $\sigma$ vs. median R after Forming with different $I_{CC}$ (b).             |

|      | Inset show $\alpha \phi$ decrease when Forming I <sub>CC</sub> increase 118      |

| 3.85 | Impact of Set $I_{CC}$ (a), $V_{BL}$ (b) and $T_{PULSE}$ (c) on Set and          |

|      | Reset (median $\pm 2\sigma$ ), with $V_{SL,Reset}=2.5V$ , $I_{CC,Reset}=2.2mA$   |

|      | and $T_{PULSE,Reset}$ =100 ns. Set $I_{CC}$ =0.4 mA, $V_{BL}$ =2V and            |

|      | $T_{PULSE} = 100$ ns were used when varying other parameters.                    |

|      | Impact of Reset $I_{CC}$ (d), $V_{SL}$ (e) and $T_{PULSE}$ (f) on Set            |

|      | and Reset (median $\pm 2\sigma$ ), with $V_{BL,Set}=2V$ , $I_{CC,Set}=0.4mA$     |

|      | and $T_{PULSE,Set}=100$ ns. Reset $I_{CC}=2.2$ mA, $V_{SL}=2.5V$ and             |

|      | $T_{PULSE} = 100$ ns were used when varying other parameters 120                 |

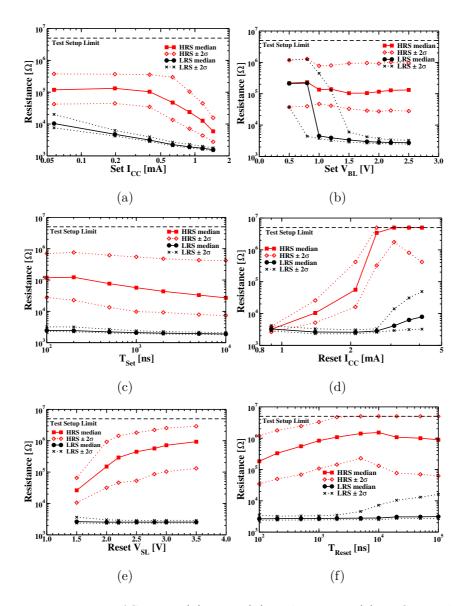

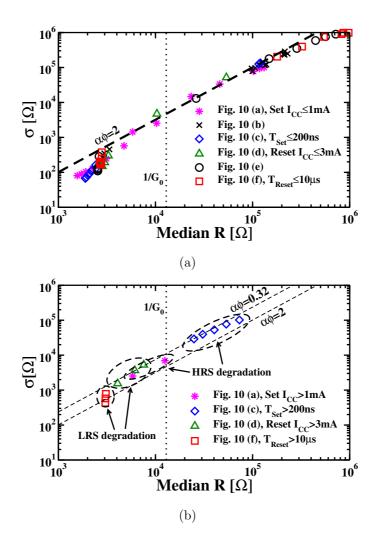

| 3.86 | $\sigma$ vs. median R in not degrading (a) and degrading (b) condi-              |

|      | tions extracted from measurements in Fig. 3.85. Degradation                      |

|      | causes $\alpha \phi$ decrease                                                    |

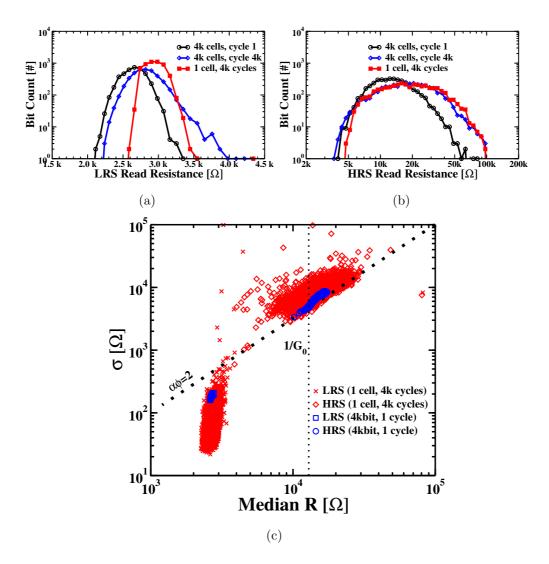

| 3.87 | Comparison of LRS (a) and HRS (b) cell-to-cell and cycle-                        |

|      | to-cycle distributions during 4k cycles with Set $I_{CC}=0.4$ mA,                |

|      | $V_{BL}=2V$ , $T_{Set} = 100$ ns and Reset $I_{CC}=2$ mA, $V_{SL}=2.5V$ ,        |

|      | $T_{Reset} = 100$ ns. $\sigma$ vs. median resistance comparison of cell-         |

|      | to-cell and cycle-to-cycle distributions (c)                                     |

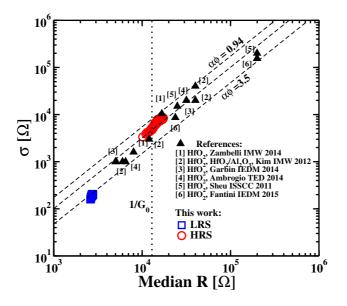

| 3.88 | $\sigma$ vs. median resistance: comparison of cycle-to-cycle distri-             |

|      | butions results with data from literature                                        |

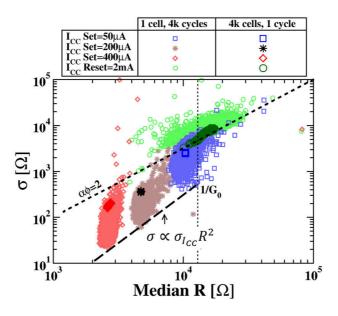

| 3.89 | Comparison of cell-to-cell and cycle-to-cycle $\sigma$ vs. median                |

|      | resistances around $1/G_0$ with different Set $I_{CC}$ , $V_{BL}=2V$ , $T_{Set}$ |

|      | = 100ns and Reset $I_{CC}$ =2 mA, $V_{SL}$ =2.5V, $T_{Reset}$ =100ns 123         |

| 3.90 | LRS and HRS median $\pm 2\sigma$ resistances measured during 2M                  |

|      | cycles performed with Set $I_{CC}=0.4$ mA, $V_{BL}=2V$ , $T_{Set}=100$ ns        |

|      | and Reset $I_{CC}=2.2$ mA, $V_{SL}=2.5$ V, $T_{Reset}=100$ ns (a). Distri-       |

|      | butions measured in different cycling conditions (b) 124                         |

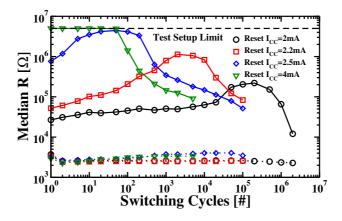

| 3.91 | Comparison of LRS and HRS median resistances in cycling<br>with Set $I_{CC}=0.4$ mA, $V_{BL}=2V$ , $T_{Set}=100$ ns, $V_{SL}=2.5V$ , $T_{Reset}=100$ ns<br>and different Reset $I_{CC}$                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

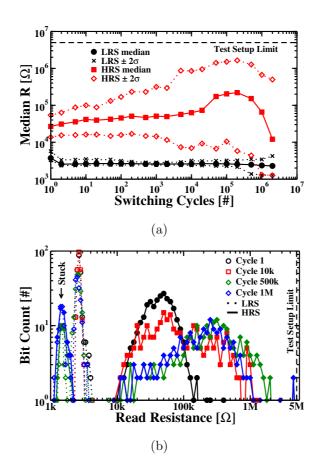

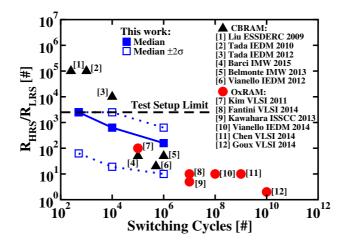

| 3.92 | $R_{HRS}/R_{LRS}$ vs. switching cycles. Median resistance $\pm 2\sigma$ results are reported and compared with literature. Limits in the test setup bound $R_{HRS}/R_{LRS}$ ratios measurement to 2500 125 |

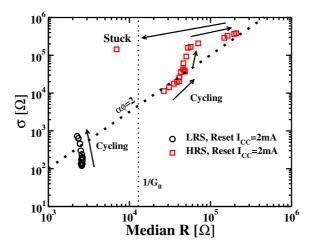

| 3.93 | $\sigma$ vs. median resistances during 2M cycles with conditions of<br>Fig. 3.90. A gradual $\sigma$ increase is observed, causing deviations<br>from $\alpha \phi$ initial value                          |

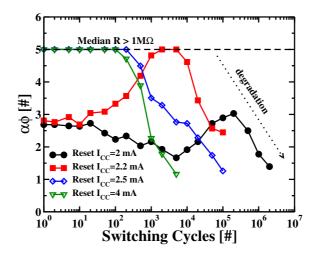

| 3.94 | $\alpha \phi$ evolution during cycling: Higher $R_{HRS}/R_{LRS}$ ratio corresponds to higher initial $\alpha \phi$ and faster degradation                                                                  |

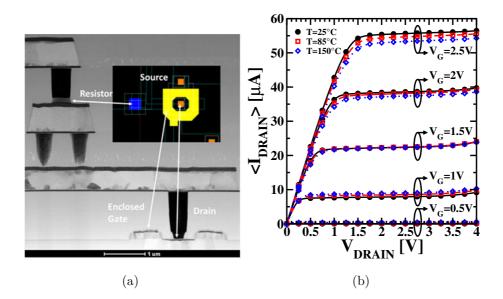

| 3.95 | TEM cross view of the Rad Hard designed 1T-1R cell (a).<br>Current-Voltage characteristics of the access ELT (b) 129                                                                                       |

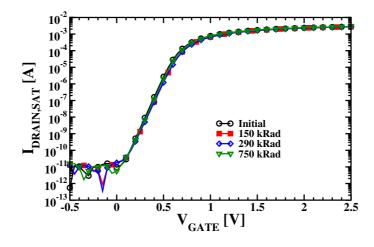

| 3.96 | Post-irradiation Current-Voltage characteristics of the access<br>ELT with varied dose rate                                                                                                                |

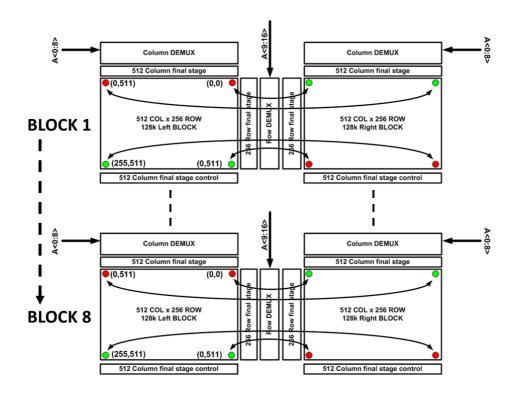

| 3.97 | The Architecture of the 1Mbit (2Mcell) test vehicle imple-<br>menting RRAM array                                                                                                                           |

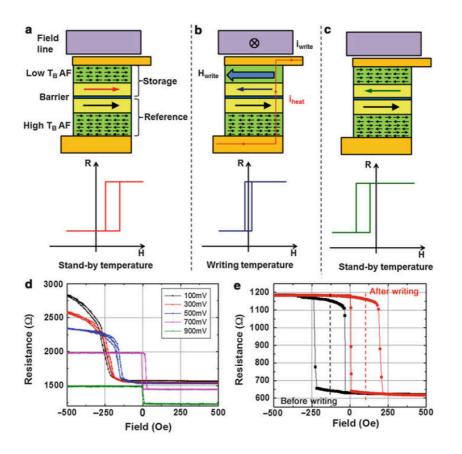

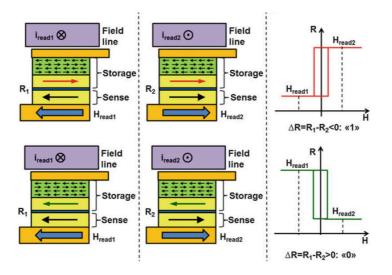

- Principle of TAS: (a) the storage layer is pinned by an an-4.1tiferromagnet with low TB at the standby temperature. (b) During writing, a current pulse is injected in the junction that heats the storage layer above TB. In that situation, the storage layer is unpinned and can be easily switched by a magnetic field generated by a single field line. (c) When the heating current is stopped, the junction cools down below TB and the storage layer is pinned by the antiferromagnet in the opposite direction. (d) MTJ with an exchange biased storage layer. Illustration of the decrease in the storage layer loop shift as a function of the heating voltage through the tunnel barrier. Note that when the heating voltage is large enough (700 mV), a small field of a few tens of Oe is sufficient to switch the storage layer magnetization. (e) Illustration of the inversion of the storage layer loop shift in standby between the initial

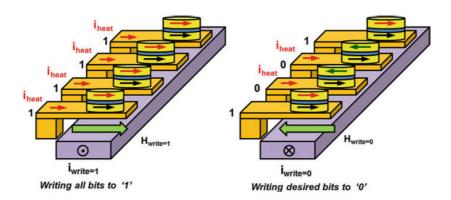

- 4.2 Multiple bits writing scheme. First, all bits are written in state '1' by injecting a heating pulse in all junctions while applying a magnetic field in the '1' direction. The heating current is then switched off for the junctions that have to be written in the '1' state and maintained in the junctions that have to be written in the '0' state. Then, the magnetic field is reversed in the '0' direction, switching all junctions that have to be written in the '0' state. This writing procedure allows writing N-bit-long words with only two magnetic fields and thus reducing the overall writing power consumption. . . . . . 136

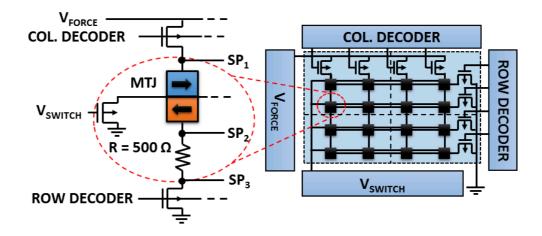

| 4.3 | Structure of a  | TAS-MRAM  | $\operatorname{cell}$ | and | its | integration | into | the |     |

|-----|-----------------|-----------|-----------------------|-----|-----|-------------|------|-----|-----|

|     | array tested in | this work | • • •                 |     |     |             |      |     | 137 |

|     |                 |           |                       |     |     |             |      |     |     |

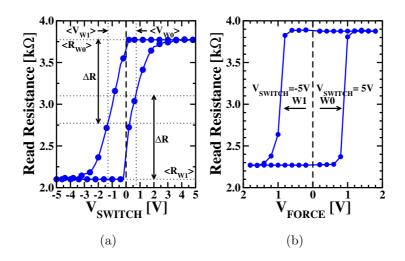

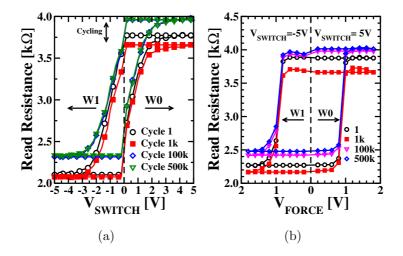

4.4  $V_{SWITCH}$  (a) and  $V_{FORCE}$  (b) hysteresis on fresh devices. . . . 139

| 4.5  | $V_{SWITCH}$ hysteresis measured during W0 and W1 operations                                                  |

|------|---------------------------------------------------------------------------------------------------------------|

|      | at different cycles with $V_{FORCE} = 1.4V$ (a). $V_{FORCE}$ hysteresis                                       |

|      | measured during W0 and W1 operations at different cycles $% \left( {{{\mathbf{w}}_{\mathbf{r}}}^{2}} \right)$ |

|      | with $ V_{SWITCH}  = 5V$ (b)                                                                                  |

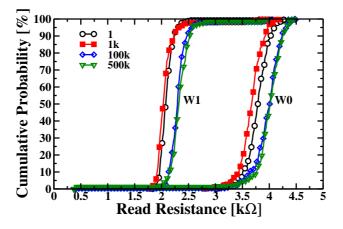

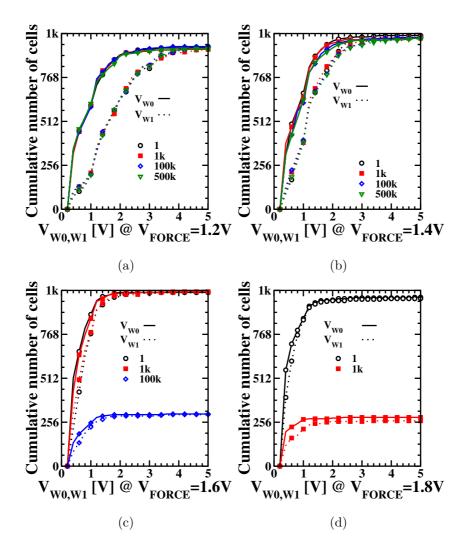

| 4.6  | $R_{W0}$ and $R_{W1}$ cumulative distributions measured during 500k                                           |

|      | cycling with $V_{FORCE} = 1.4V,  V_{SWITCH}  = 5V140$                                                         |

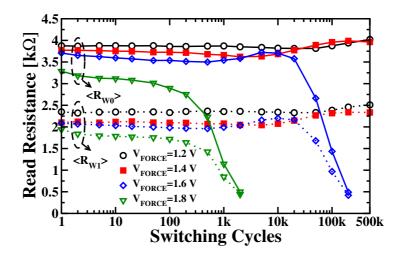

| 4.7  | $\overline{R_{W0}}$ (full lines) and $\overline{R_{W1}}$ (dotted lines) measured during 500k                  |

|      | cycling with different $V_{FORCE}$ conditions                                                                 |

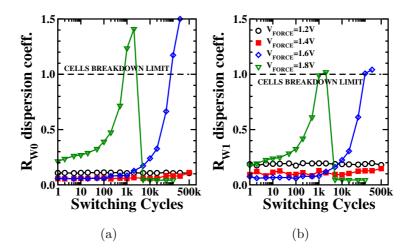

| 4.8  | $R_{W0}$ (a) and $R_{W1}$ (b) dispersion coefficients measured during                                         |

|      | 500k cycling with different $V_{FORCE}$ conditions                                                            |

| 4.9  | Cumulative number of switching cells reaching the assumed                                                     |

|      | variation $\Delta R = 1 k \Omega$ with different $V_{FORCE}$ during cycling 142                               |

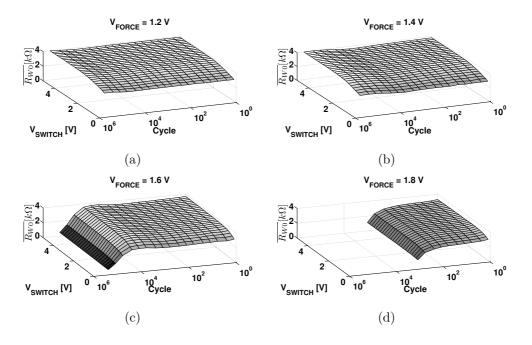

| 4.10 | 3D plot of $\overline{R_{W0}}$ as a function of $V_{SWITCH}$ and cycle number                                 |

|      | for different $V_{FORCE}$ conditions                                                                          |

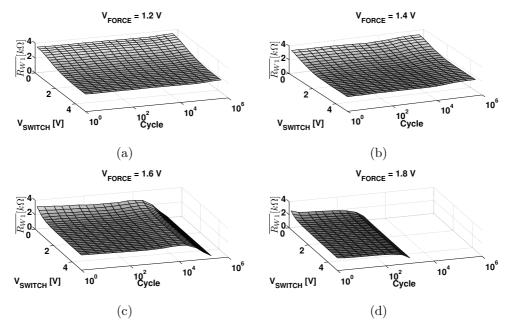

| 4.11 | 3D plot of $\overline{R_{W1}}$ as a function of $V_{SWITCH}$ and cycle number                                 |

|      | for different $V_{FORCE}$ conditions                                                                          |

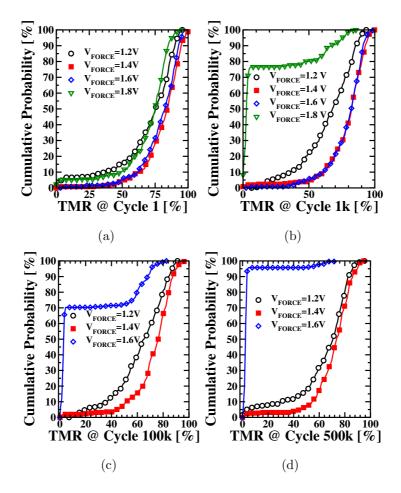

| 4.12 | TMR measured during cycling with different $V_{FORCE}$ condi-                                                 |

|      | tions at cycle 1 (a), 1k (b), 100k (c) and 500k (d) . $\ . \ . \ . \ .$ . 145                                 |

| 4.13 | Self-reference reading scheme. The sense layer is switched in                                                 |

|      | a first predetermined direction (left) and then in the oppo-                                                  |

|      | site one (middle). The MTJ resistance is measured after both                                                  |

|      | steps. The difference of resistance between the two steps, ei-                                                |

|      | ther negative (right, top) or positive (right, bottom), yields                                                |

|      | the storage layer pinning direction and thus the stored data. $$ . 146                                        |

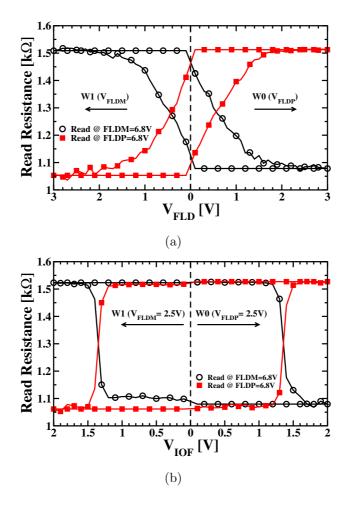

| 4.14 | FLD (a) and IOF (b) voltage hysteresis                                                                        |

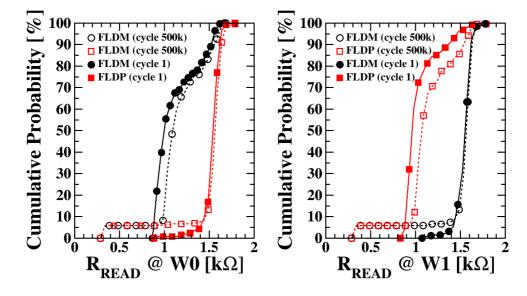

| 4.15 | Cumulative distributions of Read Resistances measured after                                                   |

|      | Write "0" (left) and Write "1" (right). $\ldots \ldots \ldots \ldots \ldots 149$                              |

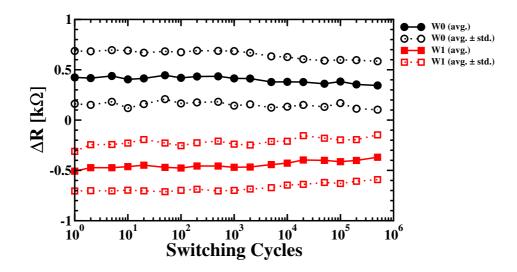

| 4.16 | Average value and standard deviations of the differential read                                                |

|      | resistances measured after Write "0" and Write "1" during                                                     |

|      | 500k endurance cycles                                                                                         |

| 4.17 | Cumulative distributions of the differential read resistances               |

|------|-----------------------------------------------------------------------------|

|      | measured after Write "0" and Write "1" at cycle 1 and after                 |

|      | 500k endurance cycles                                                       |

| 4.18 | Cumulative distributions of Read Resistances measured after                 |

|      | Write "0" and Write "1" before and after the retention tests                |

|      | on fresh (a) and cycled (b) devices                                         |

| 4.19 | Average value and standard deviations of the differential read              |

|      | resistances measured during 150 hours of retention at $160^\circ\mathrm{C}$ |

|      | and 100 hours at 200°C, on fresh (a) and cycled (b) devices                 |

|      | and comparison of average differential read resistances during              |

|      | the retention test (c)                                                      |

## List of Tables

| 2.1  | MLC standard NAND Flash coding                                                             | 12  |

|------|--------------------------------------------------------------------------------------------|-----|

| 2.2  | Architecture configurations                                                                | 23  |

| 3.1  | Summary of DC forming, pulse-induced forming, pulse-retry                                  |     |

|      | forming, DC-retry forming, Set/Reset and read voltages                                     | 35  |

| 3.2  | Summary of Forming, Set, Reset and Read parameters                                         | 53  |

| 3.3  | Forming Methods Timings and Yield                                                          | 56  |

| 3.4  | Array average read currents and Inter-cell variability after                               |     |

|      | forming with different thresholds                                                          | 57  |

| 3.5  | Forming, Set, Reset and Read Voltage Parameters                                            | 79  |

| 3.6  | Reset condition comparison. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 86  |

| 3.7  | Average and std. dev. of $\alpha$ and $\phi$ calculated on CF break cells.                 | 87  |

| 3.8  | Avge<br>rage and std. dev. of $d$ and $r$ calculated on CF break cells.                    | 88  |

| 3.9  | $G/G_0$ average and std. dev                                                               | 89  |

| 3.10 | Model parameters of the amorphous samples I-V fittings for                                 |     |

|      | both states, LRS and HRS                                                                   | 90  |

| 3.11 | Model parameters of the poly-crystalline samples I-V fittings                              |     |

|      | for both states, LRS and HRS                                                               | 91  |

| 3.12 | Processes Description                                                                      | 95  |

| 3.13 | Process and Forming Yield.                                                                 | 99  |

| 3.14 | RRAM switching parameters and variability resume extracted                                 |     |

|      | from electrical characterization.                                                          | 104 |

| 3.15 | RRAM switching parameters and variability resume extracted    |

|------|---------------------------------------------------------------|

|      | from electrical characterization                              |

| 3.16 | Resume of fundamental variability limits of filamentary based |

|      | RRAM                                                          |

| 4.1  | Read and Write operations parameters                          |

| 5.1  | Performance and reliability comparison                        |

### Chapter 1

### Introduction

Memory devices are nowadays one of the most important electronic component in the semiconductor industry. In modern day life, more and more information is being stored on computers, laptops, tablets, smartphones and more. Today this information is usually stored on Flash memory, which conquered the market in the last decade through applications like digital cameras, SD cards and USB drives and is still the mostly used nonvolatile memory technology. A growth of the memory devices storage capacity without increasing the area occupation is constantly requested by the market: in order to satisfy such requirements, an increase of the memory density and of cell shrinking is mandatory.

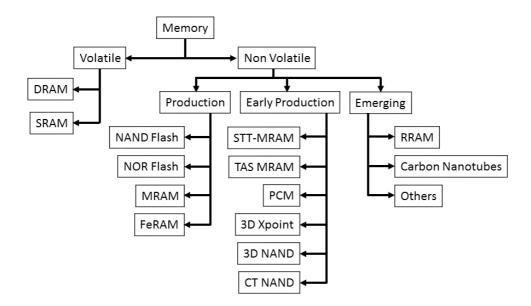

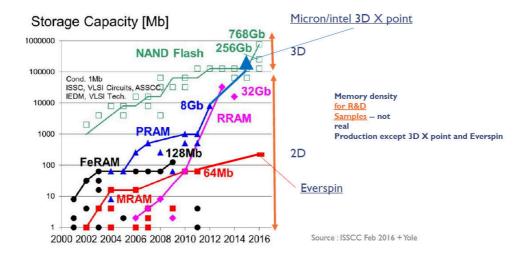

Flash technology approached its scaling limits making a significant capacity increase very challenging: to overcome this limitation, the transition from planar to three-dimensional architectures appears today as one of the most viable solution for the integration of non-volatile memory cells in Tera-bit arrays. In this framework, Charge Trap (CT) NAND memory cells are considered as one of the most promising technology for 3D integration because of a better scalability than Floating Gate (FG) NAND [1]. However, the 3D-NAND solution for increased capacity is demonstrating manufacturing difficulties and does not provide any speed, energy efficiency and reliability improvement. For this reason, several disruptive technologies have been blossoming in the last decades for non-volatile memory applications [2]: an overview of the actual memory technology scenario is provided in Fig. 1.1. The most prominent ones are Phase-Change Memories (PCM), 3D-Xpoint, Resistive RAM (RRAM) which can be divided in Oxide-based Resistive RAM (OxRAM) and Conducting-Bridge RAM (CBRAM), and Magnetic Memories (MRAM) in several fashion such as Toggle, Thermally-Assisted (TAS), Spin-Transfer Torque (STT), and perpendicular Spin-Transfer Torque (p-STT). The storage capabilities of such technologies increased rapidly in the last few years, and it is expected to be able to compete soon with NAND Flash as depicted in Fig. 1.2.

Figure 1.1: Overview of the actual memory technology scenario.

However, even if such emerging technologies offer high scalability, speed and endurance capabilities, several reliability issues still prevent them from reaching a maturity level. Reliability represents one of the major antagonist towards the unstoppable technological evolution of hyperscaled memories, since the correct operations must be assured throughout the entire lifetime. In particular, the ability of keeping unaltered the stored information even after a consistent number of write operations and for long times must be guaranteed.

In this thesis, the reliability issues affecting CT NAND, RRAM and TAS-MRAM nonvolatile memory technologies will be explored and discussed in order to understand:

- The physical mechanisms affecting the reliability

- The optimal working conditions

- The maximum performance and reliability achievable when the optimal working conditions are used (write/erase/read speed, endurance, retention, read disturb immunity, etc..)

- The expected system-level performances on different applications such as consumer/enterprise SSD, automotive, space applications.

In order to do that, results obtained trough electrical characterization of memory cells and arrays as well as physical, statistical and system modeling results will be provided and explained. Several techniques able to counteract the reliability issues will be discussed such as process optimization, read/write parameters and algorithms optimizations. Physical models will be used as a tool to correlate the experimental results with the physical phenomena causing the observed behavior of the devices, while system level models will be used to evaluate the expected system level performances in SSD applications. Finally, the thesis will speculate on promising applications and markets for each considered technology taking into account their advantages and intrinsic limitations.

### Chapter 2

### Charge Trap NAND

Charge Trap (CT) NAND memory cells are considered as one of the most promising technology for 3D integration because of a better scalability than Floating Gate (FG) NAND. Despite the high theoretical potentialities demonstrated by CT memories, several reliability issues affect such technology. Even if the transition from 2D to 3D will change the impact of the reliability issues affecting planar devices, they will still be critical. In this chapter, such reliability issues are discussed. After that, enhanced program and read techniques able to reduce their impact are presented and experimentally characterized. The results are then exploited for co-simulations at system level [3–7], assessing reliability and performance perspectives of future Solid State Drives (SSD) integrating CT-based memories.

#### 2.1 Basics

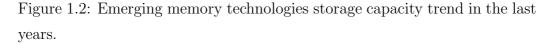

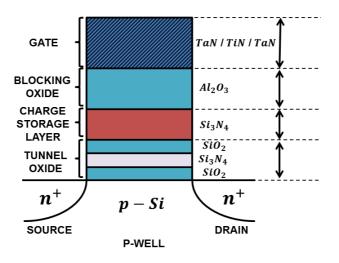

The basic concept of a Charge Trap (CT) NAND memory cell consists of a metal oxide semiconductor device where the Floating Gate (FG) is replaced by an insulating charge trapping layer [1]. Such storage layer, typically made of silicon nitride, is isolated by means of a tunnel oxide and a blocking oxide as sketched in Fig. 2.1 where the FG cell structure is reported for comparison. The tunnel oxide plays a basic role for the control of the device threshold voltage, whose value represents, from a physical point of view, the stored information. The blocking oxide prevents electrons from passing to/from the control gate. Electrons transferred into the storage layer give a threshold voltage variation. In quiescent conditions, thanks to the two oxides, the stored charge is supposed not to leak away, thus granting the nonvolatile paradigm fulfillment. Oxides are available in different materials depending on the Back-End-Of-Line (BEOL) process. The most common materials are: pure silicon dioxide (SiO<sub>2</sub>) for blocking oxides, and either SiO<sub>2</sub> or a barrier engineered stack of Oxide-Nitride-Oxide (SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub>-SiO<sub>2</sub>) for tunnel oxides. A 2D planar Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) cell is here used as example [1].

Figure 2.1: Examples of Charge Trap (a) and Floating Gate (b) devices.

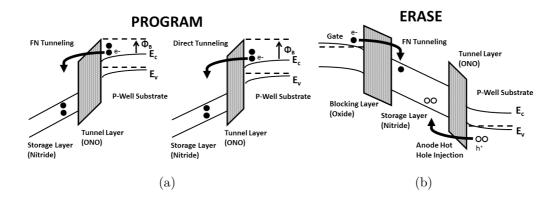

High electric fields applied to the tunnel oxide allow electron transfer across the thin insulator to the storage layer. The physical mechanism used for injecting electrons into the storage layer depends on the applied electric field and oxide barrier thickness. In case of high electric fields and large oxide barriers, injection mainly occurs through FN tunneling, whereas in case of low electric field and thin oxide barrier, electrons mainly transfer through Direct Tunneling (DT): in this case there is a higher read margin window but retention is worse [1]. In CT cells electron tunneling involves the MOS channel/substrate and it requires appropriate biasing of control gate and bulk terminals (see Fig. 2.2), while drain and source are left floating. Erase operation occurs either through electron detrapping from the storage layer or hole injection from the substrate into the storage layer; at the same time, such operation causes an electron injection from the control gate to the storage layer through FN tunneling, and this is the reason for the well-known "erase saturation" problem [8]. The results of charge separation experiments [9] demonstrate that both electron detrapping and holes injection mechanisms contribute to the erase of a previously programmed CT device: electron detrapping dominates the first part of the transient, whereas hole injection prevails after the removal of the trapped electron charge due to electron emission.

Figure 2.2: Band diagrams of tunneling mechanisms in planar SONOS CT cell during programming (a) and erase (b). The two different conditions triggering FN or DT are sketched for programming.

#### 2.2 Reliability Issues

Despite the huge potential, several reliability issues affect CT memories, especially endurance and retention.

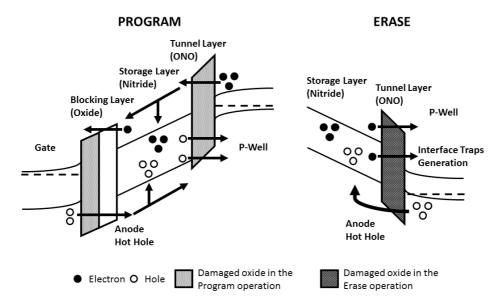

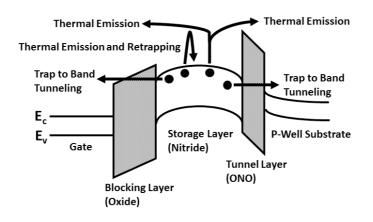

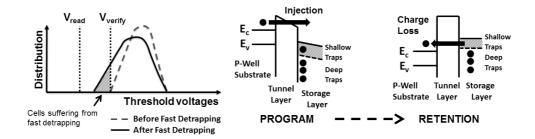

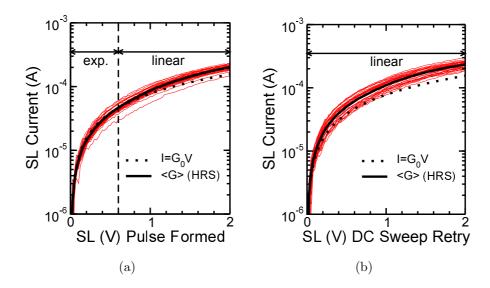

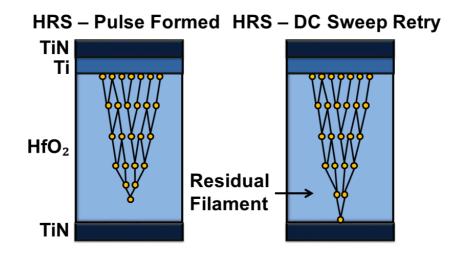

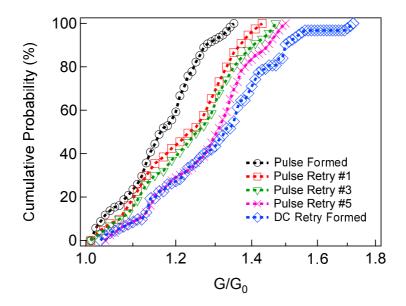

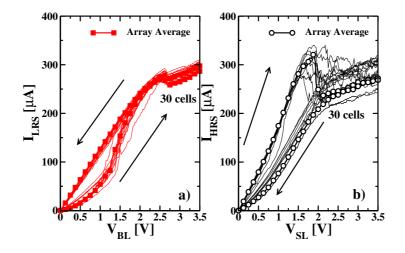

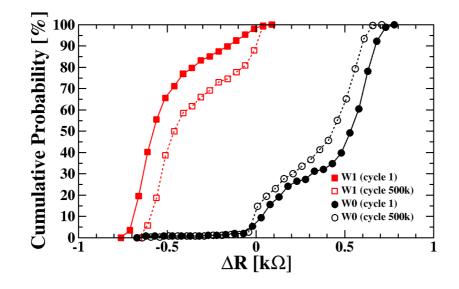

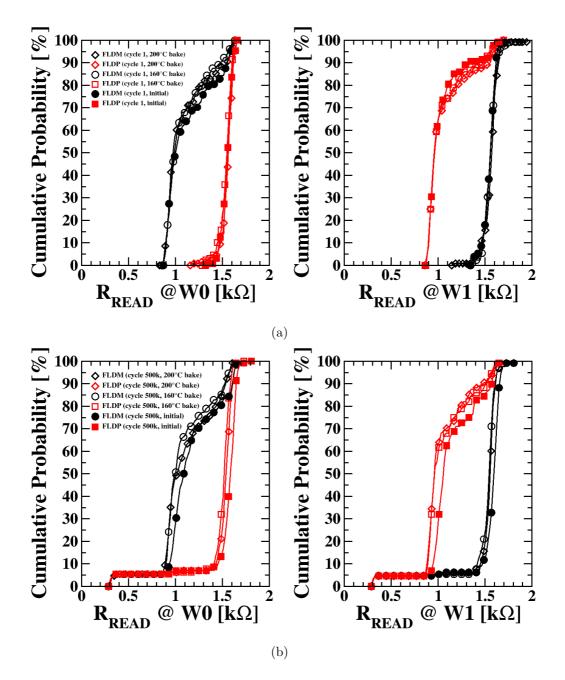

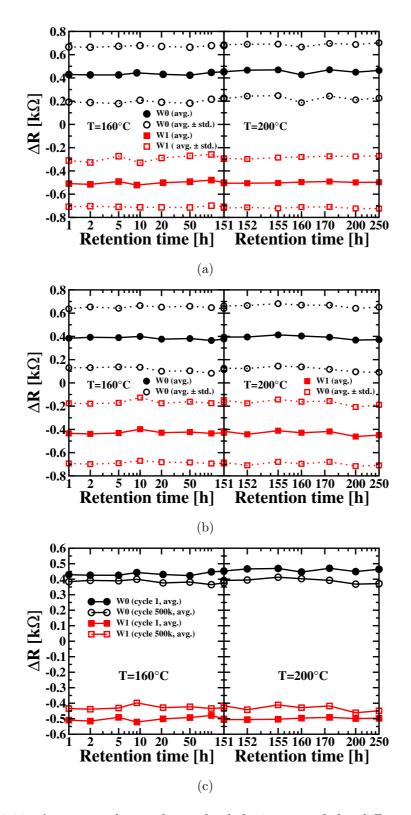

#### 2.2.1 Endurance degradation