# Scalability of Multi-Finger HEMT Performance

Giovanni Crupi, *Senior Member, IEEE*, Antonio Raffo, *Member, IEEE*, Valeria Vadalà, *Member, IEEE*, Giorgio Vannini, *Member, IEEE*, Dominique M. M.-P. Schreurs, *Fellow, IEEE*, and Alina Caddemi, *Member, IEEE*

*Abstract*—This letter aims at investigating the impact of the gate width on microwave FET performance, focusing on GaAs HEMT technology as a case study. To accomplish this complex task, the small-signal equivalent-circuit elements together with the major RF figures of merit are thoroughly analyzed for seven HEMTs based on an interdigitated layout. The gate-width impact on device performance is quantitatively and exhaustively estimated using a mathematical and systematical approach.

*Index Terms*—equivalent circuit, GaAs, high electron-mobility transistor (HEMT), multi-finger layout, scalability.

## I. INTRODUCTION

A S well known, the gate width (*W*) is a key physical parameter for microwave FET applications, since widening the active channel enables the achievement of higher output current, transconductance, and output power capability. A thorough analysis of the gate-width impact on the device performance is therefore essential for allowing device manufacturers and circuit designers to exploit advanced FET technologies at their best. The relevance of this research subject can be seen in the large number of articles dealing with the gate-width influence on microwave FET performance [1]-[8]. Although standard scaling rules can be quite straightforwardly applied to the intrinsic bias-dependent section, the specific transistor layout can critically impact the scaling of the extrinsic bias-independent section, especially when mm-wave frequencies are investigated.

The multi-finger layout is widely used to achieve wider conducting channel and, consequently, larger drain current. Thus, the total gate width is given by the product of the number of fingers ( $N_f$ ) and their length ( $W_0$ ). A key advantage of this layout consists in reducing the extrinsic gate resistance, which strongly affects the RF noise performance and the maximum frequency of oscillation ( $f_{max}$ ) [9].

Within this context, the present letter is aimed at investigating the small-signal equivalent-circuit parameters (ECPs) versus W for pseudomorphic HEMTs (pHEMTs) in GaAs technology, which is well-established and very well-

Manuscript received March 17, 2020; revised June 27, 2020; accepted July 23, 2020. This work was supported in part by the eEurostars project E!10149 MicromodGaN.

Giovanni Crupi is with the BIOMORF Department, University of Messina, 98100 Messina, Italy (e-mail: crupig@unime.it).

Antonio Raffo, Valeria Vadalà, and Giorgio Vannini are with the Department of Engineering, University of Ferrara, 44122 Ferrara, Italy.

Dominique M. M.-P. Schreurs is with the Electronic Engineering Department, KU Leuven, B-3001 Leuven, Belgium.

Alina Caddemi is with the Department of Engineering, University of Messina, 98166 Messina, Italy.

suited for mm-wave applications. In particular, the ECPs and the major RF figures of merit are analyzed to identify and quantify the impact of *W*-variations on performance, putting together new experimental data on state-of-the-art devices and well assessed results. As will be discussed, the scaling of the extrinsic ECPs can critically depend on the layout peculiarities, like the position of the via holes, and certain deviations of the intrinsic ECPs from the ideal scaling behavior can have a strong impact on device performance, like the power gain. This investigation extends our previous scaling analysis for the HEMT technology, in which the attention was focused on exploring the increase of the kink effect in  $S_{22}$  with W [10].

### **II. EXPERIMENTAL RESULTS**

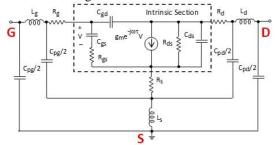

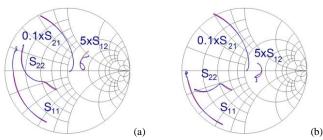

Fig. 1 depicts the equivalent circuit used for the studied multi-finger GaAs pHEMTs with a gate length of 0.15 µm and different W: 2x25 µm, 4x25 µm, 2x50 µm, 6x50 µm, 8x50 μm, 10x60 μm, and 12x60 μm. Scattering (S-) parameters have been measured from 2.5 to 65 GHz. Part of the parasitic access structures have been de-embedded from measurements by using an on-wafer thru-reflect-line (TRL) calibration [11]. This calibration process shifts the input/output reference planes from the probe tips to the gate and drain manifolds, thus eliminating probe pads and launchers and enabling determination of device behavior as when applied in a realistic microwave circuit. The extrinsic ECPs have been extracted from "cold" S-parameters (i.e.,  $V_{DS} = 0$  V) [10], [12], thereby enabling calculation of the intrinsic ECPs from the intrinsic admittance (Y-) parameters at the bias point of interest:  $V_{GS} = -$ 0.6 V and  $V_{DS} = 6$  V. Due to the well-known limitations of the "cold" modeling approach that does not allow distinguishing clearly between extrinsic and intrinsic output capacitances [12],  $C_{pd}$  is assumed to be equal to  $C_{pg}$ . As an example of the model validity, Fig. 2 compares measured and simulated Sparameters for the largest device.

Fig. 1. Small-signal equivalent circuit for the studied GaAs HEMTs.

Fig. 2. Measured (blue) and simulated (red) *S*-parameters for 720-µm device: (a) before and (b) after de-embedding the extrinsic ECPs.

Table I reports  $I_D$ , ECPs, transition frequency  $f_T$  (i.e.,  $g_m/(2\pi C_g)$  with  $C_g = C_{gs} + C_{gd}$ , and voltage gain  $A_V$  (i.e.,  $g_m/g_{ds}$ ) for the tested devices. In line with the well-known expectations that  $I_D$ ,  $g_m$ ,  $g_{ds}$ ,  $C_{gs}$ ,  $C_{gd}$ , and  $C_{ds}$  should be linearly dependent on W, their achieved good scaling allows taking the average of the gate-width normalized quantities as the reference values:  $I_{Dwav} = 0.118 \text{ mA}/\mu\text{m}, g_{mwav} = 0.454$ mS/ $\mu$ m,  $g_{dswav} = 0.017$  mS/ $\mu$ m,  $C_{gswav} = 1.259$  fF/ $\mu$ m,  $C_{gdwav} =$ 0.13 fF/ $\mu$ m, and  $C_{dswav} = 0.244$  fF/ $\mu$ m.  $R_{gs}$  exhibits the opposite trend, decreasing with W in accordance with the expectation that  $R_{gs}$  should be inversely proportional to W, but with more evident deviations, reflecting the fact that its extraction is a more challenging task. Its reference value can be estimated taking the average of  $R_{gs}W$ :  $R_{gswav} = 494 \ \Omega \mu m$ . Although  $\tau$ ,  $f_T$ , and  $A_V$  are expected to be gate-width insensitive, the obtained values show some deviations from ideal behavior, which can be attributed to fabrication tolerance. measurement uncertainty, and model approximation. To define a reference value to estimate the deviation, their average values ( $\tau_{av}$ ,  $f_{Tav}$ , and  $A_{Vav}$ ) are evaluated: 1.1 ps, 52.1 GHz, and 25.9.

Although the conventional scaling rules can be applied quite straightforwardly to the intrinsic section, they can strongly depend on the specific layout in case of the extrinsic ECPs. This is the main reason for which, in order to obtain accurate prediction capabilities, electro-magnetic (EM) approaches [5] or extraction techniques based on all the investigated peripheries are adopted. Nevertheless, to properly calibrate the EM simulator, some on-wafer test structures are required (e.g., lines having different lengths) that are not always available. The same applies to the different gate-width devices that are not necessarily all available for characterization. These considerations justify the importance of empirical scaling rules, as the ones discussed in this paper.

The anomalous value of  $C_{pg}$  for the largest device is due to the layout that is very different with respect to the other devices (see Fig. 3(d)). The different positions of via holes and how these are very adjacent to the gate/drain manifolds/fingers, thus increasing extrinsic capacitances, is well evident. As the via holes are closer to the gate than to the drain, the assumption  $C_{pd} = C_{pg}$  leads to a slight overestimation of  $C_{pd}$ , turning into a slight underestimation of  $C_{ds}$  and overestimation of  $L_d$  (see Table I). The layout with via holes closer to the actual transistor is used to optimize the area consumption for achieving a more compact device, which is a critical feature especially for large devices.

| TABLE I. PARAMETERS FOR HEMTS AT $V_{GS} = -0.6$ V AND $V_{DS} = 6$ V |        |       |       |       |       |       |       |

|-----------------------------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|

| W(µm)                                                                 | 2x25   | 4x25  | 2x50  | 6x50  | 8x50  | 10x60 | 12x60 |

| $I_D(mA)$                                                             | 5.6    | 10.3  | 11.9  | 35.4  | 51.2  | 74.3  | 86.7  |

| $C_{pg}(fF)$                                                          | 12.2   | 13.2  | 10    | 10.2  | 11.6  | 9.6   | 43.8  |

| $L_g(pH)$                                                             | 45.1   | 25.6  | 39.7  | 26.5  | 22.2  | 24.5  | 21.9  |

| $L_d(pH)$                                                             | 19.7   | 16.4  | 30    | 23.9  | 19.1  | 23.5  | 45.2  |

| $L_s(pH)$                                                             | 0      | 2.5   | 2.3   | 3.8   | 5.7   | 9.5   | 7.4   |

| $R_{g}\left( arOmega ight)$                                           | 6.5    | 3.7   | 6.2   | 1.5   | 1.4   | 0.7   | 0.7   |

| $R_d(\Omega)$                                                         | 15.9   | 7.6   | 8.3   | 1.2   | 1.7   | 0.8   | 0.9   |

| $R_s(\Omega)$                                                         | 6.3    | 3.3   | 3.4   | 0.4   | 0     | 0.1   | 0.2   |

| $g_m(mS)$                                                             | 24.5   | 47.1  | 50.1  | 131   | 171   | 254.6 | 309.6 |

| $R_{ds}(\Omega)$                                                      | 1043.9 | 554.4 | 533.2 | 195.8 | 152.1 | 100.3 | 83.6  |

| $C_{gs}(fF)$                                                          | 63.1   | 133.4 | 137.4 | 366.2 | 470.6 | 705   | 916.2 |

| $C_{gd}(fF)$                                                          | 7.7    | 15.1  | 11.5  | 36.2  | 48.7  | 69.6  | 93    |

| $C_{ds}(fF)$                                                          | 12.9   | 30.6  | 26.1  | 70.9  | 89.8  | 133.7 | 145.4 |

| $R_{gs}(\Omega)$                                                      | 4.2    | 1.4   | 1.5   | 2.5   | 1.8   | 1.4   | 0.9   |

| $\tau(ps)$                                                            | 0.86   | 0.98  | 1.05  | 1.19  | 1.14  | 1.18  | 1.32  |

| $f_T(GHz)$                                                            | 55.1   | 50.5  | 53.6  | 51.8  | 52.4  | 52.3  | 48.8  |

| $A_v$                                                                 | 25.6   | 26.1  | 26.7  | 25.6  | 26    | 25.5  | 25.9  |

| <b>S S S S S S S S S S</b>                                            |        |       |       |       |       |       |       |

Fig. 3. Photo of four analyzed devices with different gate width.

As expected [2], both  $R_d$  and  $R_s$  decrease with increasing W. However,  $R_s$  is much lower than  $R_d$  and, by enlarging W, it can reach very small values that can be even difficult to extract [13]. This is consistent with the fact that the gate is placed closer to the source than to the drain for achieving a higher breakdown voltage and maximizing extrinsic transconductance as  $R_s$  has more impact on this parameter than  $R_d$  [14].

To put the different impacts of  $N_f$  and  $W_0$  in the spotlight, we compare the results for two devices with a W of 100  $\mu$ m: 4x25 µm and 2x50 µm. Table I shows that the achieved results are quite similar, except for  $R_g$ ,  $L_g$ , and  $L_d$ , exhibiting a remarkable decrease by increasing Nf. This is consistent with the fact that a key advantage of using an interdigitated layout consists of reducing  $R_g$ . Hence, although W can be enlarged by increasing  $N_f$  and/or  $W_0$ , only a higher  $N_f$  enables reducing  $R_g$ . Such a consideration, along with the intrinsic distributed nature of the transistor behavior [15]-[19], discourages the exploitation of finger lengths above 50-60 µm at mm-wave frequencies. The behavior of  $R_e$  has been represented using the well-known scaling rule that the gate metallization resistance is proportional to  $W/N_f^2$  (i.e.,  $W_0/N_f$ ), whereas the contribution of the contact resistance is inversely proportional to W and noticeable only at small gate width [2], [9]. In [2], it has been found that  $L_g$  scales in a similar way to the gate metallization resistance, while  $L_d$  has been observed to be proportional to  $W_0/\sqrt{N_f}$  for the studied processes. Although these empirical formulas accounting for layout-dependent distributed effects cannot be straightforwardly applied to our case, they enable explanation of the observed behavior of  $L_g$  and  $L_d$ , mostly increasing with increasing  $W_0$  and reducing  $N_f$ . The largest device has a high  $L_d$  that can be ascribed to the overestimation

of  $C_{pd}$  (see above) and to the large size of the drain manifold.

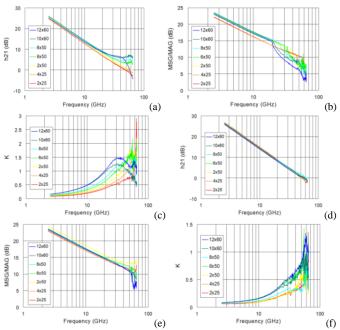

Fig. 4 shows the impact of removing the extrinsic ECPs on the measured performance: magnitude of the short-circuit current-gain  $(h_{21}),$ maximum stable/available gain (MSG/MAG), and the Rollet stability factor (K). Fig. 4(a) shows that the current-gain peak (CGP) [20] appears by increasing gate width, due to the resonance between intrinsic capacitances (i.e.,  $C_{ds}//C_g$ ) and extrinsic inductances (i.e.,  $L_d+L_s$ ). This finding is mostly a consequence of the good scaling properties of the intrinsic capacitances, leading to a reduction of the resonant frequency. The CGP appears to be less pronounced in larger devices, as can be mathematically predicted by using the definition of the damping factor ( $\zeta$ ) in terms of the equivalent-circuit elements [21]. To quantify the size of the CGP, two methods have been proposed in prior works, which are based on calculating the second order derivative of  $h_{21}$  in dB vs the frequency [22] or on estimating the area between the two  $h_{21}$  curves with and without peak [23]. Hence, depending on the given application, a proper selection of W can enable achievement of a peak in the current-gain at the frequency of interest. After de-embedding the extrinsic ECPs, CGP vanishes because of the subtraction of the extrinsic inductances.  $h_{21}$  becomes almost insensitive to W and exhibits a nearly ideal behavior that is approximately as  $g_m/(j\omega C_g)$ , rolling off with a slope of approximatively -20 dB/dec and reaching unity at a frequency very close to  $f_{Tav}$ (i.e., 52.1 GHz) (see Fig 4(d)).

Fig. 4(b) shows that the power gain drops at a rate of 10 dB/dec and then 20 dB/dec, due to the transition from MSG to MAG at the frequency where K becomes unity  $(f_K)$ . Figs. 4(c) and 4(f) illustrate that  $f_K$  is lower in larger devices, mainly due to the greater  $C_{gs}$ , and that it is increased after deembedding of the extrinsic ECPs. By comparing the power gain of the two devices having a W of 100  $\mu$ m, it is found that the device with two fingers exhibits a larger gain (see Figs. 4(b) and 4(e)). This can be attributed to the lower  $C_{gd}$  (see Table I), since MSG is given by  $|Y_{2l}/Y_{l2}|$  that at low frequencies can be approximated with  $|g_m/(j\omega C_{gd})|$ . As shown in Fig. 4(b), the power gain is found to be degraded in the two devices with a finger length of 25 µm, due to an increase of the W-normalized  $C_{gd}$  that is ascribable to the enhancement of border effects, thereby discouraging the exploitation of too short fingers.

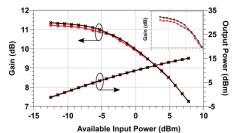

A clear and comprehensive understanding of the scaling of the small-signal parameters is an essential prerequisite for analysis and prediction of the scaling of large-signal and noise performance. Evidence of this statement can be found in the wide application of the small-signal ECPs as cornerstone for building noise and large-signal models [24-30]. As an illustrative example, Fig. 5 shows that, in line with the smallsignal analysis, the 2x50-µm device exhibits a higher power gain than that of the 4x25-µm under relatively low-power conditions. This result indicates that 2x50-µm device should be chosen for applications requiring high linearity (e.g., LNA), whereas the gain performance becomes almost  $N_{f}$ -insensitive (at constant total gate width) in strong non-linear regime.

Fig. 4. Measured (a, d)  $|h_{2l}|$ , (b, e) *MSG/MAG*, and (c, f) *K* for HEMTs with different *W*: (a, b, c) whole and (d, e, f) intrinsic devices.

Fig. 5. Measured gain and output power versus available input power at  $f_0 = 3$  GHz,  $V_{GS} = -0.6$  V, and  $V_{DS} = 6$  V in a 50- $\Omega$  environment for two 100- $\mu$ m HEMTs: (black crossed lines) 2x50  $\mu$ m and (red circled lines) 4x25  $\mu$ m.

# **III.** CONCLUSIONS

The reported empirical analysis provides microwave engineers with valuable information, simply achievable by conventional instrumentation able to measure S-parameters. The analysis can be very useful for properly choosing the device periphery, depending on the application constraints. Although the GaAs HEMT technology has been considered as a case study, the developed analysis is technology independent and extensible to other FET types. Furthermore, this study yields to outcomes that can be viewed as representative of any FET technology. On the other hand, it has been shown that the analysis of the impact of the W-scaling on microwave FET performance is not always really straightforward and of general validity as the results can strongly depend on the specific technology and layout. Even when a standard equivalent-circuit model is used, the device performance scaling can strongly depend on the combined effects of the circuit element values.

#### REFERENCES

S. W. Chen, O. Aina, W. Li, L. Phelps, and T. Lee, "An accurately scaled small-signal model for interdigitated power P-HEMT up to 50 GHz," *IEEE Trans. Microw. Theory Techn.*, vol. 45, no. 5, pp. 700-703, May 1997.

- [2] J. Wood and D.E. Root, "Bias-dependent linear scalable millimeterwave FET model," *IEEE Trans. Microw. Theory Techn.*, vol. 48, no. 12, pp. 2352-2360, Dec. 2000.

- [3] G. Crupi, D.M.M.-P. Schreurs, B. Parvais, A. Caddemi, A. Mercha, and S. Decoutere, "Scalable and multibias high frequency modeling of multi fin FETs," *Solid-State Electron.*, vol. 50, no. 10/11, pp. 1780-1786, Nov./Dec. 2006.

- [4] J.H. Oh, M. Han, S.J. Lee, B.C. Jun, S.W. Moon, J.S. Lee, J.K. Rhee, and S.D. Kim, "Effects of multigate-feeding structure on the gate resistance and RF characteristics of 0.1- m metamorphic high electronmobility transistors," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 6, pp. 1487-1493, Jun. 2009.

- [5] D. Resca, A. Raffo, A. Santarelli, G. Vannini, and F. Filicori "Scalable equivalent circuit FET model for MMIC design identified through FW-EM analyses," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 2, pp. 245-253, Feb. 2009.

- [6] T.T.-L. Nguyen and S.-D. Kim, "A gate-width scalable method of parasitic parameter determination for distributed HEMT small-signal equivalent circuit," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 10, pp. 3632-3638, Oct. 2013.

- [7] F. Zarate-Rincon, R. Murphy-Arteaga, R. Torres-Torres, A. Ortiz-Conde, and F. Garcia-Sanchez, "Modeling the impact of multi-fingering microwave MOSFETs on the source and drain resistances," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 12, pp. 3255-3261, Dec. 2014.

- [8] Y. Chen, Y. Xu, F. Wang, C. Wang, Q. Wu, S. Qiaio, B. Yan, and R. Xu, "A scalable and multibias parameter extraction method for a small-signal GaN HEMT model," *Int. J. Numer. Model. Electron. Netw. Dev. Field*, vol. 31, no. 52, e2347, Sep./Oct. 2018.

- [9] H. Rohdin, N. Moll, C.-Y. Su, and G. S. Lee, "Interfacial gate resistance in Schottky-Barrier-gate field-effect transistors," *IEEE Trans. Electron Devices*, vol. 45, no. 12, pp. 2407-2416, Dec. 1998.

- [10] G. Crupi, A. Raffo, A. Caddemi, and G. Vannini, "The kink phenomenon in the transistor S<sub>22</sub>: A systematic and numerical approach," *IEEE Microw. Wireless Comp. Lett.*, vol. 22, no. 8, pp. 406-408, Aug. 2012.

- [11] D. F. Williams, C. M. Wang, and U. Arz, "An optimal multiline TRL calibration algorithm," in *Proc. IEEE MTT-S Int. Microw. Symp. Dig.*, Philadelphia, PA, USA, Jun. 2003, pp. 1819-1822.

- [12] G. Crupi, A. Caddemi, D.M.M.-P. Schreurs, and G. Dambrine, "The large world of FET small-signal equivalent circuits," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 26, no. 9, pp. 749-762, Nov. 2016.

- [13] G. P. Gibiino, A. Santarelli, R. Cignani, P. A. Traverso and F. Filicori, "Measurement-based automatic extraction of FET parasitic network by linear regression," *IEEE Microw. Wireless Comp. Lett.*, vol. 29, no. 9, pp. 598-600, Sep. 2019.

- [14] G. Crupi, A. Raffo, V. Vadalà, G. Vannini, and A. Caddemi, "Highperiphery GaN HEMT modeling up to 65 GHz and 200°C," *Solid-State Electron.*, vol. 152, pp. 11-16, Feb. 2019.

- [15] S. Lee, P. Roblin, and O. Lopez, "Modeling of distributed parasitics in power FETs," *IEEE Trans. Electron Devices*, vol. 49, no. 10, pp. 1799-1806, Oct. 2002.

- [16] A. Cidronali, G. Collodi, A. Santarelli, G. Vannini, and G. Manes, "Millimeter-wave FET modeling using on-wafer measurements and EM simulation," *IEEE Trans. Microwave Theory Techn.*, vol. 50, no. 2, pp. 425-432, Feb. 2002.

- [17] Y. Karisan, C. Caglayan, G. C. Trichopoulos, and K. Sertel, "Lumpedelement equivalent-circuit modeling of millimeter-wave HEMT parasitics through full-wave electromagnetic analysis," *IEEE Trans. Microwave Theory Techn.*, vol. 64, no. 5, pp. 1419-1430, May 2016.

- [18] H. Aliakbari A. Abdipour, R. Mirzavand, and G. Avolio, "Large-signal distributed millimeter-wave multifinger pHEMT modeling using time-domain technique," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 27, no. 7, e21120, Sep. 2017.

- [19] D Resca, J.A. Lonac, R. Cignani, A. Raffo, A. Santarelli, G. Vannini, and F Filicori. "Accurate EM-based modeling of cascode FETs," *IEEE Trans. Microwave Theory Techn.*, vol. 58, no. 4, pp. 719-729, Apr. 2010.

- [20] G. Crupi, A. Raffo, D.M.M.-P. Schreurs, G. Avolio, A. Caddemi, and G. Vannini, "A clear-cut understanding of the current-gain peak in HEMTs: Theory and experiments," *Microw. Optl Techn. Lett.*, vol. 54, no. 12, pp. 2801-2806, Dec. 2012.

- [21] S. A. Ahsan, S. Ghosh, S. Khandelwal, and Y. S. Chauhan, "Pole-zero approach to analyze and model the kink in gain-frequency plot of GaN HEMTs," *IEEE Microw. Wireless Comp. Lett.*, vol. 27, no. 3, pp. 266-268, Nov. 2017.

- [22] G. Crupi, A. Raffo, Z. Marinković, G. Avolio, A. Caddemi, V. Marković, G. Vannini, and D. M. M.-P. Schreurs, "An extensive experimental analysis of the kink effects in S<sub>22</sub> and h<sub>21</sub> for a GaN HEMT," *IEEE Trans. Microwave Theory Techn.*, vol. 62, no. 3, pp. 513-520, Mar. 2014.

- [23] M. A. Alim, M. A. Hasan, A. A. Rezazadeh, C. Gaquiere, and G. Crupi, "Multi-bias and temperature dependence of the current-gain peak in GaN HEMT," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 30, no. 4, e22129, Apr. 2020.

- [24] A. Caddemi, G. Martines and M. Sannino, "HEMT for low noise microwaves: CAD oriented modeling," *IEEE Trans. Microw. Theory Techn.*, vol. 40, no. 7, pp. 1441-1445, Jul. 1992.

- [25] J. Gao, C. L. Law, H. Wang, S. Aditya, and G. Boeck, "A new method for pHEMT noise-parameter determination based on 50-Ω noise measurement system," *IEEE Trans. Microw. Theory Techn.*, vol. 51, no. 10, pp. 2079-2089, Oct. 2003.

- [26] F. Danneville, "Microwave noise and FET devices," *IEEE Microw. Mag.*, vol. 11, no. 6, pp. 53-60, Oct. 2010.

- [27] D. E. Root and B. Hughes, "Principles of nonlinear active device modeling for circuit simulation," in *Proc. 32nd ARFTG Conference Digest*, Tempe, AZ, USA, Dec. 1988, pp. 1-24.

- [28] A. Jarndal and G. Kompa, "An accurate small-signal model for AlGaN-GaN HEMT suitable for scalable large-signal model construction," *IEEE Microw. Wireless Comp. Lett.*, vol. 16, no. 6, pp. 406-408, Jun. 2006.

- [29] G. Avolio, A. Raffo, I. Angelov, G. Crupi, A. Caddemi, G. Vannini, and D. M. M.-P. Schreurs, "Small- versus large-signal extraction for charge models of microwave FETs," *IEEE Microw. Wireless Comp. Lett.*, vol. 24, no. 6, pp. 394-396, June 2014.

- [30] Y. Xu, C. Wang, H. Sun, Z. Wen, Y. Wu, R. Xu, X. Yu, C. Ren, Z. Wang, B. Zhang, T. Chen, and T. Gao, "A scalable large-signal multiharmonic model of AlGaN/GaN HEMTs and its application in C-band high power amplifier MMIC," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 8, pp. 2836-2846, Aug. 2017.