## Università degli Studi di Ferrara

DOTTORATO DI RICERCA IN "SCIENZE DELL'INGEGNERIA"

CICLO XXIV

COORDINATORE Prof. Stefano Trillo

## DESIGN TECHNIQUES FOR HIGH-EFFICIENCY MICROWAVE POWER AMPLIFIERS

Settore Scientifico Disciplinare ING-INF/01

**Dottorando** Dott. Di Falco Sergio **Tutore** Prof. Vannini Giorgio

(firma)

(firma)

Anni 2009/2011

Per una vita a colori, insieme...

## Contents

| Preface:    |                                                    |                                                                   | vii |  |

|-------------|----------------------------------------------------|-------------------------------------------------------------------|-----|--|

| Prefazione: |                                                    |                                                                   | ix  |  |

| Chapter 1   | Mic                                                | rowave power amplifier design techniques                          | 1   |  |

| Prefazione: | Introduction                                       |                                                                   |     |  |

|             | 1.1                                                | Load-Pull design approach                                         | 4   |  |

|             | 1.2                                                | Iterative Harmonic balance analysis approach                      | 7   |  |

|             | 1.3                                                | Nonlinear modeling for microwave power amplifier design           | 9   |  |

|             | Con                                                | clusion                                                           | 11  |  |

|             | Refe                                               | erences                                                           | 13  |  |

| Chapter 2   | A new approach to microwave power amplifier design |                                                                   |     |  |

|             | Introduction                                       |                                                                   |     |  |

|             | 2.1                                                | A low-frequency large-signal measurement setup                    | 20  |  |

|             |                                                    | 2.1.1 Investigation of low-frequency dispersion                   |     |  |

|             |                                                    | by exploiting the proposed setup                                  | 22  |  |

|             |                                                    | 2.1.2 Large-signal measurements for high-efficiency operation     | 26  |  |

|             | 2.2                                                | The proposed design approach                                      | 31  |  |

|             |                                                    | 2.2.1 Class-A power amplifier design example                      | 37  |  |

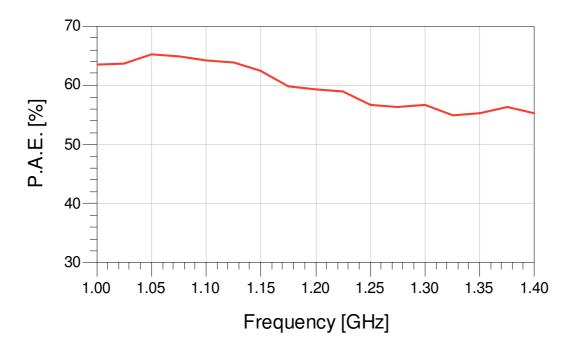

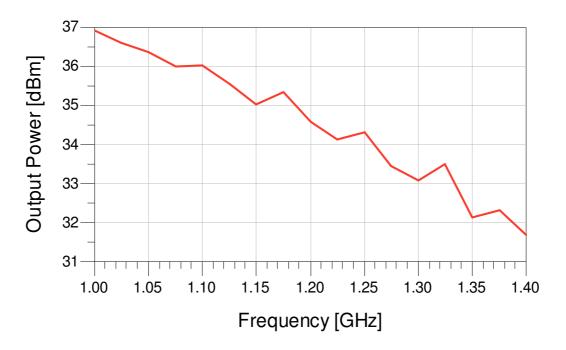

|             |                                                    | 2.2.2 Wideband Class-AB power amplifier design example            | 40  |  |

|             | 2.3                                                | Power amplifier design accounting for input large-signal matching | 44  |  |

|             |                                                    | 2.3.1 Power amplifier design and realization                      | 45  |  |

|             | Conclusion                                         |                                                                   |     |  |

|             | References                                         |                                                                   |     |  |

| Chapter 3   | Higi                                               | h-efficiency power amplifier design                               | 53  |  |

| Chapter 3   | Introduction                                       |                                                                   |     |  |

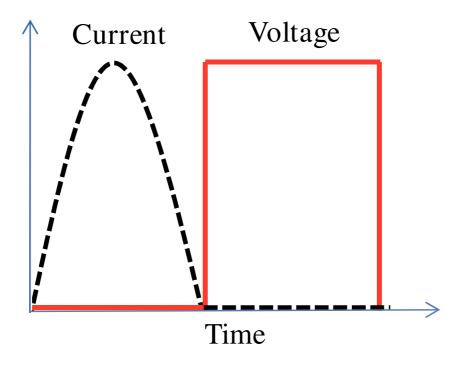

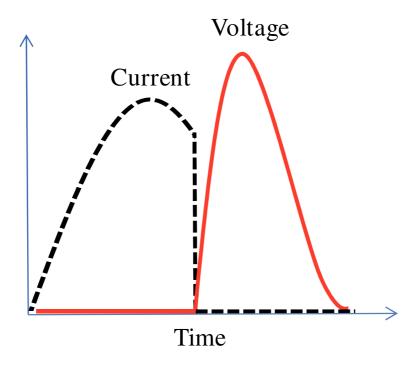

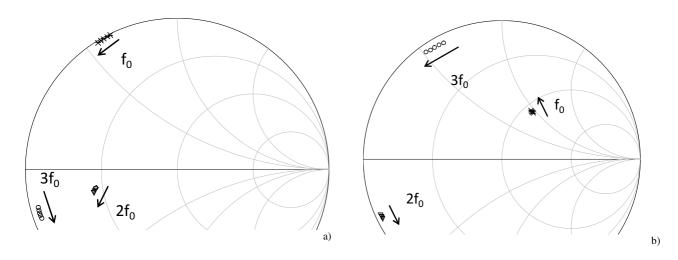

|             | 3.1                                                | Design scenario for class-F and class-E power amplifiers          | 56  |  |

|             | 3.2                                                | Class-F power amplifier design                                    | 58  |  |

|             | 3.3                                                | Class-E power amplifier design                                    | 67  |  |

|             | Conclusion                                         |                                                                   |     |  |

|             | References                                         |                                                                   | 74  |  |

#### Contents

| Chapter 4                                  | Degradation phenomena of electron devices |                                                   |     |  |

|--------------------------------------------|-------------------------------------------|---------------------------------------------------|-----|--|

|                                            | in m                                      | 77                                                |     |  |

|                                            | Intro                                     | 79                                                |     |  |

|                                            | 4.1                                       | The innovative measurement system                 | 80  |  |

|                                            | 4.2                                       | Analysis of the gate current as a suitable        |     |  |

|                                            |                                           | indicator for GaAs FET degradation                | 81  |  |

|                                            |                                           | 4.2.1 Theoretical overview                        | 82  |  |

|                                            |                                           | 4.2.2 Experimental results and considerations     | 83  |  |

|                                            | 4.3                                       | Empirical study of performance                    |     |  |

|                                            |                                           | degradation of X-band GaN HEMTs                   | 92  |  |

|                                            |                                           | 4.3.1 DC characterization                         | 92  |  |

|                                            |                                           | 4.3.2 Low-frequency large-signal characterization | 94  |  |

|                                            |                                           | 4.3.3 Small-signal characterization               | 96  |  |

|                                            | Con                                       | clusions                                          | 98  |  |

|                                            | Refe                                      | erences                                           | 99  |  |

| General conclusion<br>List of publications |                                           |                                                   | 101 |  |

|                                            |                                           |                                                   | 103 |  |

| Ringraziame                                | 105                                       |                                                   |     |  |

### Preface

The increasingly diffusion of wireless devices during the last years has established a sort of "second youth" of analog electronics related to telecommunication systems. Nowadays, in fact, electronic equipments for wireless communication are exploited not only for niche sectors as strategic applications (e.g., military, satellite and so on): as a matter of fact, a large number of commercial devices exploit wireless transmitting systems operating at RF and microwave frequencies.

As a consequence, increasing interest has been focused by academic and industrial communities on RF and microwave circuits and in particular on power amplifiers, that represent the core of a wireless transmitting system. In this context, more and more challenging performance are demanded to such a kind of circuit, especially in terms of output power, bandwidth and efficiency.

The present thesis work has been focused on RF and microwave power amplifier design that, as said before, represents one of most actual and attractive research theme. Several aspects of such topic have been covered, from the analysis of different design techniques available in literature to the development of an innovative design approach, providing many experimental results related to realized power amplifiers. Particular emphasis has been given to high-efficiency power amplifier classes of operation, that represent an hot issue in a world more and more devoted to the energy conservation. Moreover, electron device degradation phenomena were investigated, that although not directly accounted for, represent a key issue in microwave power amplifier design.

In particular, the first chapter of this thesis provides an overview of commonly adopted design methodologies for microwave power amplifier, analyzing the advantages and the critical aspects of such approaches. Moreover, nonlinear device modeling issues oriented to microwave power amplifier design have been dealt with.

In the second chapter, an innovative design technique is presented. It is based on experimental electron device nonlinear characterization, carried out by means of a low-frequency large signal measurement setup, in conjunction with the modeling of high-frequency nonlinear dynamic phenomena. Several design examples have been carried out by exploiting the proposed approach that confirm the effectiveness of the design technique.

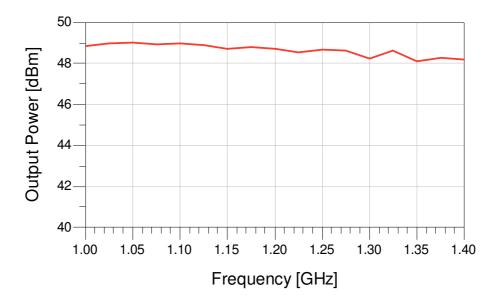

In the third chapter, the proposed design methodology has been applied to high-efficiency power amplifier classes of operations, that need to control the device terminations not only at the fundamental frequency, but also at harmonics. Two high-efficiency power amplifiers have been realized by adopting such a technique, demonstrating performance in terms of output power and efficiency comparable with the state of the art.

Finally, in chapter four an important power amplifier design aspect has been dealt with, related to degradation and performance limitation of microwave electron devices. Several experimental results have been carried out by exploiting a new measurement setup, oriented to the characterization of degradation phenomena of microwave electron devices.

## Prefazione

Negli ultimi anni, la crescente diffusione dei sistemi wireless ha segnato una sorta di "seconda giovinezza" dell'elettronica analogica. Diversamente da quanto accadeva fino a qualche anno fa, le apparecchiature elettroniche che sfruttano sistemi di telecomunicazioni senza fili non sono necessariamente legate a settori di nicchia, come per esempio quelli militari o per applicazioni spaziali: oggigiorno infatti, la maggior parte dei dispositivi elettronici commerciali, dai telefoni cellulari ai tablet PC, integrano al loro interno sistemi wireless che operano a radiofrequenza o a microonde.

Tale contesto ha suscitato un altrettanto crescente interesse scientifico, sia accademico che legato ai settori di ricerca industriali, sui circuiti operanti a radiofrequenza e a microonde ed, in particolare, sugli amplificatori di potenza, che rappresentano l'elemento cardine di un sistema di trasmissione senza fili e ai quali sono richieste prestazioni sempre più stringenti in termini di potenza, efficienza e banda operativa.

L'oggetto di questa tesi di dottorato riguarda appunto la progettazione di amplificatori di potenza operanti a microonde, che, come detto in precedenza, rappresenta uno dei temi di ricerca più attuali e interessanti. In particolare, si sono analizzate diverse tecniche di progettazione presenti in letteratura, evidenziandone i vantaggi e gli aspetti più critici, arrivando all'introduzione di una nuova metodologia di progetto che supera le limitazioni delle tecniche di progetto più comuni. Tale metodologia è basata su misure sperimentali a bassa frequenza effettuate sfruttando un sistema di misura innovativo e a basso costo, garantendo comunque, grazie all'impiego di una adeguata descrizione degli effetti reattivi, lo stesso livello di accuratezza ottenibile con costosi sistemi di misura operanti a microonde, come dimostrato dai diversi risultati sperimentali proposti.

Particolare enfasi è stata dedicata al progetto di amplificatori di potenza ad alta efficienza, argomento di particolare interesse scientifico in virtù della crescente sensibilità relativa alle tematiche legate al risparmio energetico. Inoltre, è stato approfondito il problema del degrado delle prestazioni dei dispositivi elettronici che, sebbene non sia direttamente preso in considerazione dai progettisti di amplificatori di potenza, rappresenta un tema centrale nella progettazione di tali circuiti.

Nello specifico, nel corso del primo capitolo verranno analizzate approfonditamente le tecniche di progettazione di amplificatori di potenza presenti in letteratura, affrontando anche tematiche di modellistica di dispositivi elettronici per applicazioni a microonde.

#### Prefazione

Nel secondo capitolo, verrà presentata una metodologia di progetto innovativa, basata sulla caratterizzazione sperimentale di dispositivi elettronici in congiunzione con il modeling degli effetti non lineari dinamici degli stessi. Diversi risultati sperimentali verranno forniti a dimostrazione dell'efficacia della tecnica di progettazione proposta.

Nel terzo capitolo, la metodologia di progetto sviluppata verrà applicata alle classi di funzionamento ad alta efficienza, che prevedono il controllo delle terminazioni dell'amplificatore non solo alla frequenza fondamentale, ma anche alle sue armoniche. Inoltre, verranno descritti nel dettaglio il progetto e la realizzazione di due amplificatori di potenza ad alta efficienza operanti a microonde, progettati adottando la tecnica proposta, che hanno dimostrato prestazioni in termini di potenza ed efficienza in linea con lo stato dell'arte.

In conclusione, nel quarto capitolo si analizzeranno i fenomeni di degrado e le limitazioni delle prestazioni che coinvolgono i dispositivi elettronici orientati alla progettazione di amplificatori di potenza per applicazioni a microonde. Anche in questo caso, la trattazione sarà corredata da diverse evidenze sperimentali, ottenute sfruttando un sistema di misura sviluppato all'uopo.

## Chapter 1

Microwave power amplifier design techniques Microwave power amplifier design techniques

## Introduction

During the last decades, microwave circuits have found a growing diffusion due to the increasing number of electronic systems, from commercial devices (e.g., smartphone, personal computer) going to strategic applications (e.g., radar, satellite), that exploit wireless transmitting systems operating at microwave frequencies.

In this scenario, microwave power amplifiers play a crucial role since they represent the key component of a transmitting chain: as a matter of fact, overall performance of the entire transmitting system strongly depends on the performance of such a kind of circuit.

To date, the great advantages introduced by solid state technology, in terms of costs, size of the circuit and so on, have progressively replaced the vacuum tube domain in microwave power amplifier development: as a consequence, increasing interest of both academic and industrial research community has been focused on more- or less-conventional solid state power amplifier (SSPA) design methodologies, based on both mature (e.g., GaAs) or emerging (e.g., GaN) technologies, in order to meet the severe requirements of the modern wireless transmitting systems.

In this chapter, commonly adopted design strategies for microwave SSPAs will be treated, pointing out the advantages and the critical aspects of such methodologies, that are usually based on both experimental characterization of the electron device (e.g., high-frequency load-pull measurements) and iterative harmonic balance analysis, performed by exploiting computer aided design (CAD) simulators.

Moreover, nonlinear modeling of electron devices oriented to microwave application will be briefly discussed, focusing on the issues related to the design of microwave power amplifiers.

## 1.1 Load-Pull design approach

One of the crucial design facet of a microwave high power amplifier is to find out the correct input and output terminations that ensure adequate performance. Such a task is made highly hard due to the nonlinear behavior of the active electron devices, that represent the keystone of power amplifier operation under large signal conditions.

A typical and widely used approach in order to characterize the nonlinear behavior of an active electron device and consequently adopted for design of a high power amplifier, is represented by load/source-pull measurements [1-5]. The great advantage of adopting such a technique is represented by the capability of testing the electron device under actual large signal operating conditions: fixed the bias condition, the load/source-pull technique, in fact, consists in varying source and load impedances of a device under test (DUT), while simultaneously measuring the DUT performance at different input driving stimuli. Thus, measurement data collected by exploiting the load/source-pull technique, can be directly used in order to obtain information about the optimal source and load impedances for a specific electron device class of operation.

Load pull measurement systems can be classified in two main categories, depending on the technique adopted for the impedance synthesis [6]: *passive* and *active* load pull setups.

In traditional passive load pull systems, in order to synthesize the required source and load impedances, mechanical or electrical tuners (that consist of passive networks) are exploited. On the other hand, in the active systems, the required terminations are set by adopting a couple of phase-and amplitude- controlled RF signal generators.

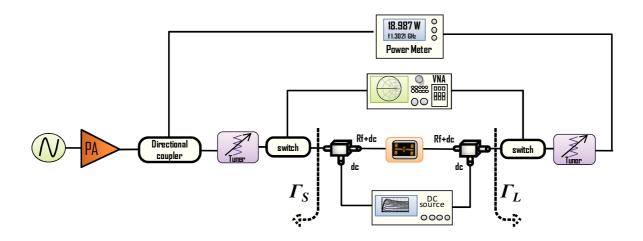

Fig. 1.1 shows a block diagram of a passive load-pull measurement system:

Fig. 1.1 Typical configuration of Load/source-pull passive measurement system

The input signal is monitored by a directional coupler and measured by a power meter. The input tuner is exploited in order to optimize the input match assuring the maximum power delivery to the device. The reflection coefficient  $\Gamma_S$ , that is the actual source impedance, can be set to any desired value within a certain region of the Smith chart, depending on the frequency of operation besides the system capabilities. At the output port another tuner allows to set  $\Gamma_L$ : as well as  $\Gamma_S$ , load reflection coefficient  $\Gamma_L$  can be set within a limited portion of the Smith chart. The second channel of the power meter is exploited in order to measure the output power delivered by the DUT, whereas the bias is supplied by a DC source through a couple of bias tees.

Passive load pull systems need a power- and frequency-calibration before performing measurements. The calibration of the setup is carried out through a VNA: all the setup portions have to be characterized in terms of two ports S-parameters in order to properly evaluate impedance and power levels at the DUT planes. The power level is calibrated by a power meter measurement with the DUT replaced by a thru connection.

After calibration, a standard de-embedding technique can be used to calculate the correct quantities. Load-pull measurements are exploited in order to trace power contours on the Smith chart, which represents a very powerful tool that provides information on the best performance achievable by the device. A constant performance parameter (i.e. power, PAE, etc.) can be displayed as a curve of corresponding measured impedances on the Smith chart.

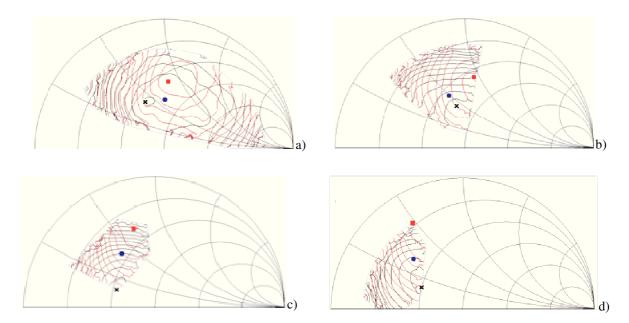

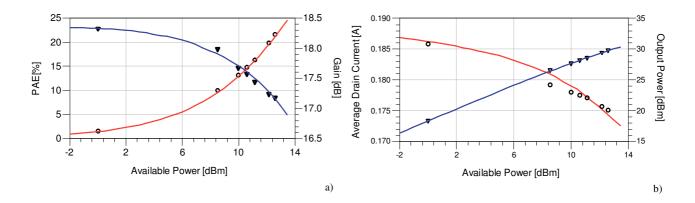

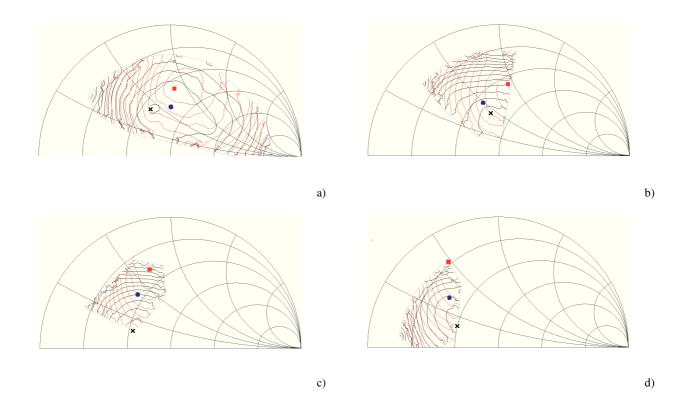

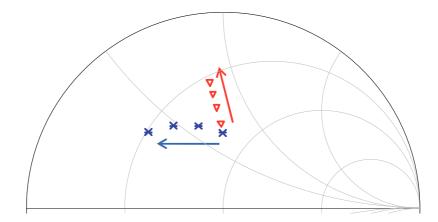

An example of contours obtained by measurements carried out at different frequencies through a passive load pull measurement system [3] is shown in fig. 1.2:

Fig. 1.2. Output-power (black) and efficiency (red) contours measured by means of a 4–26 GHz load-pull setup (at 2.5 dB gain compression) at 4 GHz a), 5 GHz b), 6 GHz c), and 7 GHz d) fundamental frequency. Best output power (cross) and best PAE (square) terminations.

#### Microwave power amplifier design techniques

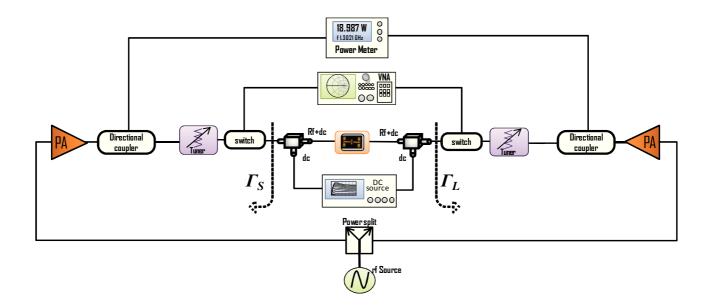

Fig 1.3 shows a diagram of an active load/source-pull system. A large amplitude signal is provided by the RF signal generator and is divided into two signals that drive each port of the DUT. The two variable attenuators and the phase shifter control the power levels and the relative phase of the two incident waves at the input and output ports. Before the signal reaches the network analyzer bidirectional couplers, switches and filters work on lowering the power level of the signal itself to avoid damage of the instrumentation. Isolators are used to protect sensitive components from the high power levels. As well as for the passive load-pull, calibration is also needed for the active one.

Fig. 1.3 Typical configuration of Active load/source- pull passive measurement system

Another classification regarding load/source-pull setups can be made on the basis of the nature of the measured quantities, i.e. whether information of device figures of merit are acquired through a *scalar* or *vectorial* techniques. Typical scalar systems, as the previously described setups, are generally based on the acquisition of the magnitude of input and output power trough a power meter (or in alternative through a spectrum analyzer). On the other hand, vectorial systems are based on the acquisition of both magnitude and phase of the electrical quantities of interest; consequently, time domain waveforms referred to the DUT terminals can be measured exploiting such a kind of setups and, for this reason, they are generally called *time-domain load-pull systems*.

The time-domain load-pull approach combines the advantages to characterize the DUT under actual large-signal operation together with the knowledge of time-domain current and voltage waveforms at the device ports, enabling to perform waveform engineering technique [7] for microwave power amplifier design.

In order to obtain time-domain waveforms, two different approaches can be followed: samplerbased or mixer-based methodology [8]. A sampler-based measurement instrument uses samplers to perform the down conversion of the high-frequency signals to the IF spectrum and is hence based on the harmonic sampling principle. The large-signal network analyzer (LSNA) is an example of a sampler-based measurement instrument [9-11]. On the other hand, a mixer-based measurement instrument uses the heterodyne principle, which exploits mixers to downconvert the RF signals to the IF spectrum. This principle can be found in the nonlinear vector network analyzer (NVNA) [12], [13]. Recently, a third approach has been developed [14], that exploits an high performance oscilloscope in order to directly acquire time-domain electrical waveforms at microwave frequencies.

Although load-pull systems represent one of the most common aid in power amplifier design, they exhibit some critical aspects. Dealing with load-pull passive architectures, they suffer from the inability in synthesizing the full range of DUT terminations, in particular when very low impedances are needed for on-wafer devices having a large periphery. On the other hand, although active systems overcome such a limitation by adopting active load synthesis, they may become critical from the stability point of view [15].

Moreover, both architectures are frequency and power limited and their cost dramatically increases when high operating power and frequencies are required or when harmonic termination control is needed (e.g., high efficiency power amplifier design).

Finally, when performing load-pull measurements exploiting both scalar or vectorial setups, no information is given about the intrinsic device load-line: loading conditions which show similar microwave performance, in fact, can correspond to very different load-lines at the intrinsic device. This is a vital aspect, for example, for safe operation since reliability conditions are defined at the intrinsic DUT ports [16] as the passive access structures to the active area do not have any major impact on reliability.

# **1.2 Iterative Harmonic balance analysis approach**

CAD simulations represent another diffused paradigm for microwave power amplifier design. Since such a kind of circuit is usually designed in order to work under nonlinear periodic regime, generally harmonic-balance simulators are adopted. The harmonic balance represents the main analysis technique exploited to solve nonlinear microwave circuits in steady-state conditions.

#### Microwave power amplifier design techniques

The original Harmonic-balance algorithm [17-20], applied to the solution of nonlinear electronic circuits, combines both time- and frequency-domain approaches, taking the benefits related to the respective representations. More precisely, the initial nonlinear circuit to solve, that is described by nonlinear equations inferred by combining the Kirchhoff laws and the constitutional relationship of each element of the circuit, is split in two subnetworks: in the first one, that is treated exploiting a time-domain technique, all nonlinear elements are gathered; on the other hand, a frequency domain approach is selected for the second network, that contains the linear portion of the circuit. The two subnetworks are connected through ports, whose number depends on the number of the nonlinear elements. With the aim of *balancing* the two subnetworks, the electrical variables at these ports are represented by their Fourier description and the results of the analysis of both subcircuits are combined minimizing the balancing errors at each harmonic component. With the advent of MMIC circuits which exploit a relatively large number of active devices, Harmonic-balance equations are more conveniently defined on a circuit-node basis.

Harmonic-balance algorithm is implemented in almost all commercial microwave CAD simulators, providing a powerful tool for power amplifier design: as a matter of fact, iterative harmonic-balance analysis could overcome the need for expensive load-pull measurement setups since load-pull contours could be traced using simulation results only.

However, iterative harmonic-balance design approach relies on availability of an electron device nonlinear model. Generally, electron device models oriented to microwave CAD applications are the so called empirical models, that represent the best solution for CAD simulations of a nonlinear circuit.

The identification of an empirical model is based on measurements carried out on the fabricated device. Moreover, they may include some knowledge of the physical structure of the device and they are usually referred as equivalent-circuit models, or they may be a powerful and flexible extrapolating/interpolating scheme, and referred as black-box models.

One of the most important limitations of harmonic-balance design approaches is strictly related on the accuracy of the electron device model adopted. In practice, the identification of a global and accurate model of an electron device oriented to microwave power amplifier design is a very hard task, due to the strong nonlinearities involved in the device behavior. As a matter of fact, electron device models, available for example from the foundries, provide accurate nonlinear performance predictions in a relatively narrow neighborhood of given bias and load conditions [21]. As a consequence, a designer is usually forced in considering a mix of design approaches, based on both large-signal experimental characterization of the electron device and iterative harmonic balance analyses.

# **1.3 Nonlinear modeling for microwave power amplifier design**

Commonly adopted active devices for microwave power amplifier are represented by high electron mobility transistors (HEMTs) [22], that are field effect devices particularly suited for such an application due to their superior performance in terms of power, noise and maximum operating frequency. HEMTs for microwave applications are generally based on III-V compounds, as gallium arsenide (GaAs), that represents a mature technology and for many years the main resource in high-frequency applications, or gallium nitride (GaN), an emerging technology that is the strong candidate for high-power high-efficiency power amplifiers due to its higher breakdown voltage and operative temperature.

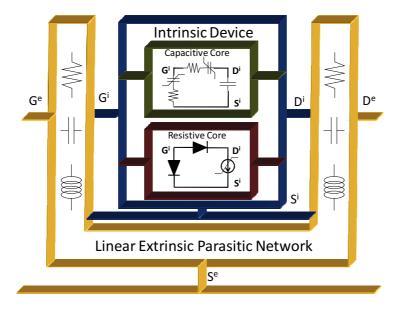

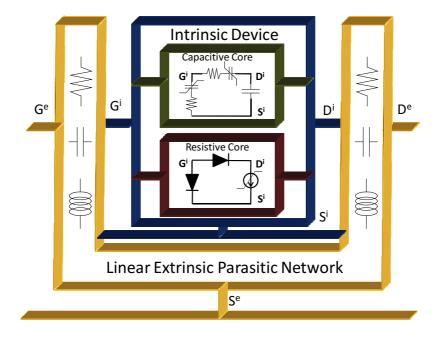

A simplified model topology of a HEMT device and, in general, of a field effect transistor (FET) is proposed in Fig. 1.4.

The linear extrinsic parasitic network in Fig. 1.4 describes the access passive structure to the device active area and accounts for metallization and dielectric losses as well as for associated inductive and capacitive effects. Its correct modeling is a fundamental issue to obtain accurate model predictions. Parasitic elements can be characterized by exploiting conventional lumped descriptions [23-24], which can be identified by only using small-signal measurements, or, alternatively, by adopting electro-magnetic simulations of the device layout [25-26].

As clearly shown in Fig. 1.4, the "intrinsic device" can be divided into two parts, which can be considered strictly in parallel: a "capacitive core" describing the nonlinear dynamic phenomena, and a "resistive core" accounting for the dc and low-frequency (LF) I/V device characteristics. The latter one differ from the dc response due to surface state densities, deep-level traps and thermal phenomena.

The ED resistive core modeling is extremely complex, not only because a number of important nonlinear phenomena must be considered (e.g., breakdown, forward conduction of the gate-source diode, knee of the IV curves, etc..) but also due to the non negligible presence of dispersive effects [27-31], which, de facto, impose the exploitation of nonlinear dynamic measurements in order to obtain good prediction capabilities.

In order to probe further this issue we must consider that the drain and gate currents at the intrinsic ED ports, above the cut-off of LF dispersive effects (i.e., some hundreds of kilohertz) but at frequencies low enough to neglect the reactive effects related to the capacitive core, can be expressed as follows:

$$i_{g}(t) = h(\underline{\nu}(t), P_{0}, \theta_{case})$$

$$i_{d}(t) = f(\underline{\nu}(t), \underline{V}_{0}, P_{0}, \theta_{case})$$

$$(1)$$

In (1), *h* and *f* are two algebraic (i.e., memory-less) functions,  $\underline{v}$  is the vector of the intrinsic voltages,  $\underline{V}_0$  its average value,  $\underline{P}_0$  the average dissipated power, and, lastly,  $\Theta_{case}$  is the device case temperature.

Fig. 1.4: Nonlinear equivalent circuit for an FET Electron Device.

The dependence on  $\underline{V}_0$  accounts for the influence of traps and surface state densities [27-31], while  $\underline{P}_0$  and  $\Theta_{case}$  determine, through the thermal resistance, the device I/V characteristic dependence on the junction temperature.

Identification of (1), in particular the drain current equation, is quite a prohibitive task mostly due to the complex dependence on its large number of controlling variables. Moreover, traps and thermal effects cannot be separately dealt with, both because the time constants of those phenomena are not always different and also since the device thermal state influences the trapping state [28]. Thus identification of (1) necessarily requires the introduction of suitable approximations to make the problem affordable.

As far as the capacitive core is concerned, dispersive phenomena due to traps and thermal behavior represent second order effects (whose evidence has rarely been dealt with in the literature [22]) regularly neglected in electron device models oriented to power amplifier design [22], [32-35]. A  $\pi$  model of capacitors is often adopted for the capacitive core description, nevertheless better prediction capabilities can be obtained at higher frequencies by introducing gate-source and gate-drain RC series, as shown in Fig.1.4, to describe nonquasi-static effects which accounts for a finite device memory time [22], [32-33]. Other nonquasi-static phenomena can be described in terms of trans-capacitances or delay times.

Provided a careful de-embedding of the parasitic network is carried out, small-signal, bias/frequency-dependent S-parameter measurements are usually sufficient to accurately determine the voltage-dependent capacitive-core parameters. These ones can be "fitted" trough suitable analytical expressions, or directly stored into look-up tables [34-37] to build a nonlinear dynamic model. Even problems related to charge conservation, although dealt with in the literature, do not seem to represent a major problem once suitable expedients are adopted [38-40].

Dealing with the resistive core behavior, a number of modeling approaches have been proposed in the literature [27-31] both based on look-up tables or analytical expressions. Some of them introduce assumptions which enable the models to be identified on the basis of bias-dependent dc and ac small-signal differential measurements carried out above the cut-off of low-frequency dispersion. However, in practice, model accuracy is commonly improved by exploiting in the identification phase, besides ac and dc measurements, also large-signal dynamic measurements as, for instance, pulsed IV characteristics [41-42].

Despite the use of quite expensive, special-purpose pulsed I/V setup's, the identification of an accurate, global model for the resistive core still remains a very complex and hard task and this justifies why foundry models often properly work in a limited number of given quiescent bias conditions: typically, a limited set of pulsed I/V measurements is fitted. Such a kind of approach inevitably leads to local models which cannot provide accurate information outside the range of the few quiescent bias conditions considered. This clearly represents a strong limitation in power amplifier design based on harmonic-balance analysis.

### Conclusion

In this first chapter, a panoramic view of commonly adopted design methodologies for microwave power amplifiers has been provided, putting in evidence both advantages and limitations in adopting the described approaches. Particular attention has been paid to design techniques based on the experimental characterization of the ED through large-signal measurement setups and on the harmonic-balance analysis. Moreover, an overview of ED nonlinear modeling issues oriented to microwave power amplifier design has been given.

In the next chapter, an innovative design technique will be described, that overcomes the limitations of the methodologies described in this chapter, combining the main advantages related to each technique.

## References

- [1] J.M. Cusak, S.M. Perlow, B.S. Perlman, "Automatic load contour mapping for microwave power transistors," IEEE Trans. On Microw. Theory and Tech., vol. 22, no. 12, pp.1146-1152, Dec. 1974.

- [2] A. Ferrero, V. Teppati, "Accuracy Evaluation of On-Wafer Load-Pull Measurements," in Proc. IEEE 55th ARFTG Microwave Measurements Conference, Boston, 2000, pp. 1–5.

- [3] Focus Microwaves Data Manual, Focus Microwaves Inc., Montreal, Canada, 1988.

- [4] M.N. Tutt, D. Pavlidis, C. Tsironis, "Automated On-Wafer Noise and Load Pull Characterization Using Precision Computer Controlled Electromechanical Tuners," in Proc. IEEE 37th ARFTG Microwave Measurements Conference, Boston, 1991, pp. 66–75.

- [5] P. Colantonio, F. Giannini, E. Limiti, High Efficiency RF and Microwave Solid State Power Amplifiers, New York: J. Wiley & Sons, 2009.

- [6] J.E. Muller, B. Gyselinckx, 'Comparison of active versus passive on-wafer load-pull characterisation of microwave and mm-wave power devices', IEEE MTT-S Intern. Microwave Symp. Digest, Vol. 2, May 1994, pp. 1077–1080.

- [7] P. J. Tasker, "Practical waveform engineering," IEEE Microwave Mag., vol. 10, no. 12, pp. 65-76, December 2009.

- [8] W. Van Moer, L. Gomme "NVNA versus LSNA: enemies or friends?," IEEE Microwave Mag., vol. 11, no. 1, pp. 97-103, Feb. 2010.

- [9] W. Van Moer and Y. Rolain, "A large-signal network analyzer: Why is it needed?," IEEE Microwave Mag., vol. 7, no. 6, pp. 46–62, Dec. 2006.

- [10] T. Van den Broeck and J. Verspecht, "Calibrated vectorial nonlinear network analyzer," in IEEE MTT-S Int. Microwave Symp. Dig., San-Diego, CA, 1994, pp. 1069–1072

- [11] Maury microwave. http://maurymw.com/products/rfdcs/lsna/lsna1.htm

- [12] P. S. Blockley, D. Gunyan, and J. B. Scott, "Mixer-based, vectorcorrected, vector signal/network analyzer offering 300 kHz–20- GHz bandwidth and traceable phase response," in IEEE MTT-S Int. Microwave Symp. Dig, June 2005, p. 4.

- [13] Agilent PNA-X Series, 5989-8041EN, May 2009.

- [14] Mesuro Limited. <u>http://www.mesuro.com/technology.htm</u>

- [15] F. Giannini, G. Leuzzi, Nonlinear Microwave Circuit Design. Chichester, England: Wiley, 2004.

- [16] A. Raffo, V. Di Giacomo, P.A. Traverso, A. Santarelli, G. Vannini, "An Automated Measurement System for the Characterization of Electron Device Degradation under Nonlinear Dynamic Regime," IEEE Trans. Instrum. Meas., vol. 58, no. 8, pp.2663-2670, Aug. 2009.

- [17] M. Urabe, 'Galerkin's procedure for nonlinear periodic systems,' Arch. Rational Mech. Anal., Vol. 20, 1965,pp. 120–152.

- [18] E.M. Baily, 'Steady state harmonic analysis of nonlinear networks,' PhD Thesis, Stanford University, CA, 1968.

- [19] M.S. Nakhla, J. Vlach, 'A piecewise harmonic balance technique for determination of periodic response ofnonlinear systems,' IEEE Trans. Circuits Syst., Vol. CAS-23, N. 2, Feb. 1976, pp. 85–91.

- [20] V. Rizzoli, A. Lipparini, E.Marazzi, 'A general-purpose program for nonlinear microwave circuit design', IEEE Trans. Microwave Theory Tech., Vol. MTT-31, N. 9, Part I, Sept. 1983, pp. 762–769.

- [21] F. De Groote, J.-P. Teyssier, O. Jardel, T. Gasseling, J. Verspecht, "Introduction to measurements for power transistor characterization," IEEE Microwave Mag., vol. 9, no. 3, pp. 70–85, Jun. 2008.

- [22] M. J. Golio, Microwave MESFETs and HEMTs, Artech House, 1991.

- [23] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," IEEE Trans. Microw. Theory Tech., vol. 36, no. 7, pp. 1151–1159, Jul. 1988.

- [24] N. Rorsman, M. Garcia, C. Karlsson and H. Zirath "Accurate small signal modeling of HFET's for millimeter-wave applications," IEEE Trans. Microw. Theory Tech., vol. 44, no. 3, pp. 432-437, Mar. 1996.

- [25] B. Cetiner, R. Coccioli, B. Housmand, and T. Itoh, "Combination of circuit and full wave analysis for prematched multifinger FET," in Proc. 30th Eur. Microw. Conf., Paris, 2000, pp. 1–4.

- [26] D. Resca, A. Santarelli, A. Raffo, R. Cignani, G. Vannini, F. Filicori, D.M.M.-P. Schreurs, "Scalable Nonlinear FET Model Based on a Distributed Parasitic Network Description," IEEE Trans. Microw. Theory and Tech., vol. 56, no. 4, pp. 755-766, Apr. 2008.

- [27] A. Raffo, A. Santarelli, P.A. Traverso, M. Pagani, F. Palomba, F. Scappaviva, G. Vannini, F. Filicori, "Accurate PHEMT Nonlinear Modeling in the Presence of Low-Frequency Dispersive Effects," IEEE Trans. Microw. Theory and Tech., vol. 53, no. 11, pp. 3449-3459, Nov. 2005.

- [28] A. Raffo, V. Vadalà, G. Vannini, A. Santarelli, "A new empirical model for the characterization of lowfrequency dispersive effects in FET electron devices accounting for thermal influence on the trapping state," in Proc. IEEE MTT-S Int. Microwave Symp., Atlanta, 2008, pp. 1421–1424.

- [29] W. Struble, S.L.G. Chu, M.J. Schindler, Y. Tajima, J. Huang, "Modeling intermodulation distortion in GaAs MESFETs using pulsed I-V characteristics," in Proc. GaAs IC Symposium, Monterey, 1991, pp. 179 – 182

- [30] T. Roh, Y. Kim, Y. Suh, W. Park, B. Kim, "A simple and accurate MESFET channel-current model including bias-dependent dispersion and thermal phenomena", IEEE Trans. Microw. Theory and Tech., vol.45, no. 8, pp. 1252 1255, Aug. 1997.

- [31] C. Camacho-Penalosa, "Modeling frequency dependence of output impedance of a microwave MESFET at low frequencies," Electron. Lett., vol. 21, no.12, pp. 528 529, Jun. 1985.

- [32] A. Jarndal and G. Kompa, "Large-signal model for AlGaN/GaN HEMTs accurately predicts trappingand self-heating-induced dispersion and intermodulation distortion," IEEE Trans. Electron Devices, vol. 54, no. 11, pp. 2830-2836, Nov. 2007.

- [33] I. Angelov, N. Rorsman, J. Stenarson, M. Garcia, H. Zirath, "An empirical table-based FET model," IEEE Trans. Microw. Theory and Tech., vol 47, no. 12, pp. 2350-2357, Dec. 1999.

- [34] G. Crupi, D.M.M.-P. Schreurs, Dongping Xiao, A. Caddemi, B. Parvais, A. Mercha, S. Decoutere, "Determination and Validation of New Nonlinear FinFET Model Based on Lookup Tables," IEEE Microw. Wireless Compon. Lett., vol. 17, no.5, pp. 361 - 363, May 2007.

- [35] A. Santarelli, V. Di Giacomo, A. Raffo, P.A. Traverso, G. Vannini, F. Filicori, "A Nonquasi-Static Empirical Model of Electron Devices," IEEE Trans. Microw. Theory Tech., vol. 54, no. 12, pp. 4021– 4031, Dec. 2006.

- [36] M. Fernández-Barciela, P. J. Tasker, Y. Campos-Roca, M. Demmler, H. Massler, E. Sanchez, M. C. Curras-Francos, and M. Schlechtweg, "A simplified broadband large signal non quasi-static table-based FET model," IEEE Trans. Microw. Theory Tech., vol. 48, no. 3, pp. 395–405, Mar. 2000.

- [37] F. Filicori, A. Santarelli, P. A. Traverso, A. Raffo, G. Vannini, M. Pagani, "Non-linear RF device modelling in the presence of low-frequency dispersive phenomena", Int. J. RF Microw. Comput.-Aided Eng., Vol. 16, no 1, pp. 81-94, Jan. 2006.

- [38] D. E. Root, "Nonlinear charge modeling for FET large-signal simulation and its importance for IP3 and ACPR in communication circuits," in Proc. 44th IEEE Midwest Circuits Systems Symp., vol. 2, pp. 768-772, Aug. 2001.

- [39] R. Follmann, D. Kother, A. Lauer, R. Stahlmann, I. Wolff, "Consistent large signal implementation of capacitances driven by two steering voltages for FET modeling," in Proc. 35th Eur. Microwave Conf., Paris, 2005, [CD-ROM].

- [40] I. Kallfass, H. Schumacher, T.J. Brazil, "A Unified Approach to Charge-Conservative Capacitance Modelling in HEMTs," IEEE Microw. Wireless Compon. Lett., vol. 16, no. 12, pp. 678 680, Dec 2006.

- [41] J. Scott, J. G. Rathmell, A. Parker, M. Sayed, "Pulsed device measurements and applications," IEEE Trans. Microw. Theory and Tech., vol. 44, no. 12, pp. 2718-2723, Dec. 1996.

- [42] J. Rodriguez-Tellez, T. Fernandez, A. Mediavilla, A. Tazon, "Characterization of Thermal and Frequency-Dispersion Effects in GaAs MESFET Devices," IEEE Trans. Microw. Theory and Tech., vol. 49, no. 7, pp. 1352 – 1355, Jul. 2001.

Microwave power amplifier design techniques

## Chapter 2

A new approach to microwave power amplifier design A new approach to microwave power amplifier design

## Introduction

In the previous chapter, an overview of commonly adopted design methodologies for microwave power amplifier has been presented. High-frequency large-signal setups have been dealt with. Although they represent the most common aid for power amplifier design since electron devices are characterized under actual operating conditions, however they are frequency and power limited, and their cost dramatically increases when high operating power and/or frequencies are required. On the other hand, it was pointed out that the availability of an accurate model could overcome the need for experimental measurements (e.g. load-pull measurements) by using simulation results only: unfortunately, the identification of a global and accurate electron device model is a very hard task due to its nonlinear behavior.

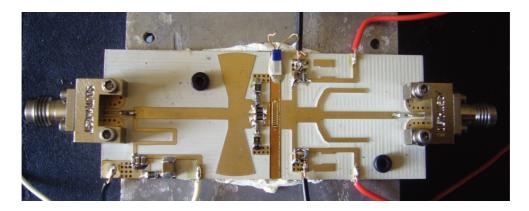

In this chapter, a nonlinear measurement system based on low-frequency multi-harmonic excitation will be presented, that allows to characterize the electron device behavior under large signal operation. Such a setup enables given source/load terminations at fundamental and harmonic frequencies to be easily synthesized and results particularly suited to investigate low-frequency dispersion phenomena (i.e., long-term memory effects) affecting microwave devices. To this end, several experimental results based on GaN devices will be discussed.

In this chapter, an original approach to power amplifier design will be also introduced, which overcomes the major limitations of commonly adopted design methodologies discussed in the previous chapter. Such a technique is mainly based on low-frequency nonlinear experimental device characterization, carried out by exploiting the mentioned large signal setup, and shows the same level of accuracy provided by high-frequency large-signal measurements. In order to demonstrate

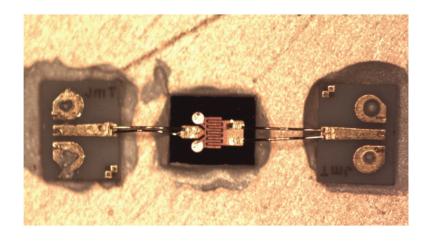

the effectiveness of the proposed design technique, several power amplifier examples will be proposed and the design and realization of a wideband hybrid high-power amplifier, based on a 20mm GaN power bar, will be deeply investigated.

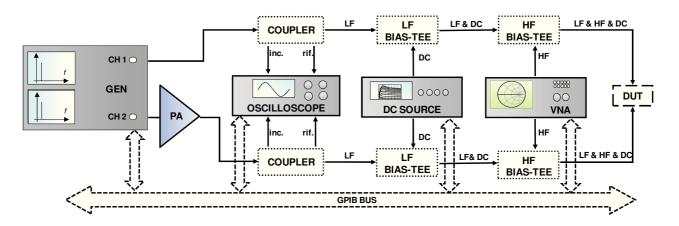

## 2.1 A low-frequency large-signal measurement setup

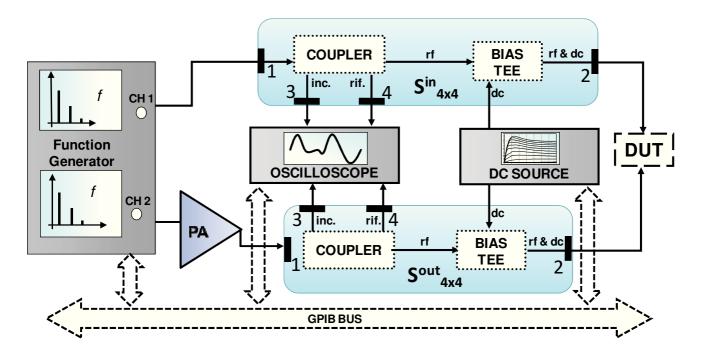

The architecture of the proposed large-signal low-frequency measurement system is shown in Fig. 2.1. In particular, the function generator has two 50-ohm channels that can independently provide arbitrary waveforms in the frequency range [1 mHz - 120 MHz]. To overcome the power limitation of the function generator, a 30-W power amplifier is cascaded to the channel devoted to the device output port excitation. Two wideband (10 kHz - 400 MHz) dual directional couplers monitor the DUT incident and reflected waves which are acquired by means of a four channel digital oscilloscope (4 GSa/s). A high resolution (4  $\mu$ V; 20 fA) and accurate (V: 0.05%, I: 0.2%) DC source provides the bias for the DUT. To ensure DC and RF path isolation, two wideband (200 kHz - 12 GHz) bias-tees are used.

Fig. 2.1: Block diagram of the proposed measurement system.

In order to characterize only the device resistive core, that accounts for DC and low frequency I/V device behavior, it is necessary to operate at frequencies where the dynamic effects associated to charge storage variations and/or finite transit times can be neglected. Moreover, it is of primary

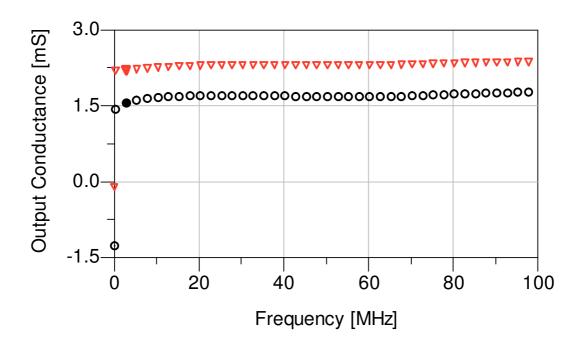

interest to characterize device response above the cut-off of low-frequency dispersion (this is why pulsed setups exploit very short pulse duration). To this end, a 2 MHz fundamental frequency has been found adequate for the considered electron devices. The validity of such a choice has been verified on the basis of S-parameter measurements carried out, in the frequency range [300 kHz – 98 MHz], by exploiting a low-frequency VNA. More precisely, Fig. 2.2 shows the measured output conductance, for a 0.25- $\mu$ m GaN HEMT device having a periphery of 400  $\mu$ m, under two different bias conditions corresponding respectively to class-A and AB operation. In the same figure also the output conductance DC values are reported to highlight that frequency variations in the range [2 MHz – 98 MHz] are negligible. This confirms that a 2 MHz frequency is sufficient to operate above the cut-off of low-frequency dispersion coherently with the large number of papers (e.g., [1]) devoted to microwave device characterization where pulsed measurements with pulse width of 500 ns or longer have been adopted.

Fig. 2.1: 400- $\mu$ m GaN HEMT output conductance versus frequency for two different bias conditions:  $V_{g0} = -3 V$ ,  $V_{d0} = 20 V$  (triangles), and  $V_{g0} = -2 V$ ,  $V_{d0} = 25 V$  (circles). The filled symbols represent the output conductance value at 2 MHz.

In the selected frequency range, all the measurement setup components satisfy linear nondistortion conditions. This greatly simplifies the setup calibration procedure which practically consists in the experimental characterization of the two 4-port networks ( $S_{in}^{4x4}$  and  $S_{out}^{4x4}$ ) shown in Fig. 2.1. The characterization can be carried out by adopting the same procedure that has been fully detailed in [2] or, alternatively, by simply exploiting a low-frequency VNA.

#### A new approach to microwave power amplifier design

The measurement setup has been automated via an IEEE488 standard interface by means of a commercial instrument automation software. The graphical user interface (Fig. 2.2) of the control software enables measurements to be carried out in an automated way: the user can define the dc parameters, in terms of a bias grid (voltage or current) and related compliances, in accordance with the device safe operating area. The two channels of the signal generator, which sets the incident signals applied to the device ports, are controlled in an independent way: for each one, the user can define the fundamental frequency component and the number of harmonics. For maximum level of flexibility, the user can arbitrarily define amplitude and phase for each spectral component.

Fig. 2.2: Graphical user interface of the control software.

### 2.1.1 Investigation of low-frequency dispersion by exploiting the proposed setup

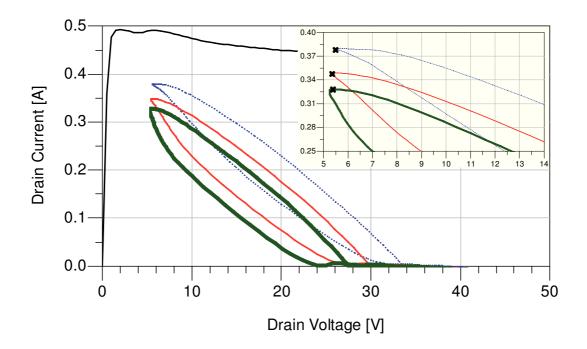

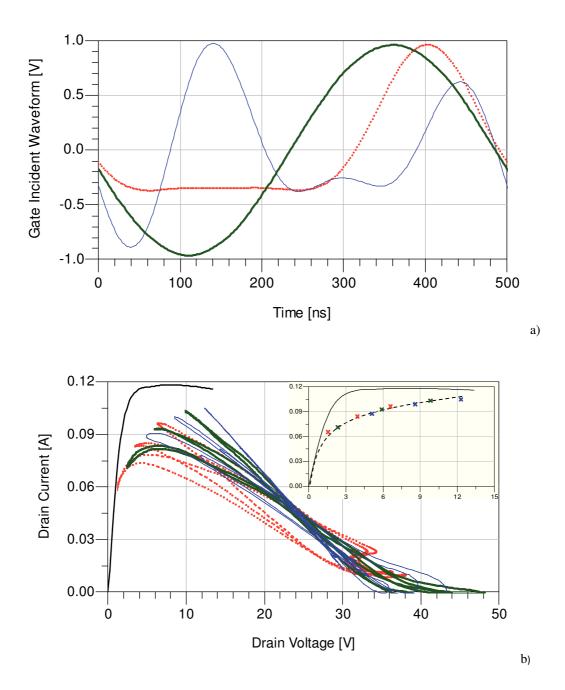

The proposed measurement setup can be effectively used for in-depth investigation of the complex mechanisms related to low-frequency dispersion. For example, the low-frequency measurements shown in Fig. 2.3, carried out on a  $0.7 \times 800 \ \mu\text{m}^2$  GaN HEMT, highlight the current collapse dependence on the average value of the gate voltage V<sub>g0</sub>. The crosses in the enlarged view within the inset correspond to the same values of the instantaneous voltages (v<sub>g</sub> = 0 V, v<sub>d</sub> = 5.4 V); if low-frequency dispersion were not present, the same instantaneous current value (corresponding

to the dc one) should be measured. Instead, it is well evident that as the quiescent gate voltage  $V_{g0}$  moves into the off state region the instantaneous drain current goes down.

Fig. 2.3: Measurements performed by exploiting the new large-signal measurement system on a 800- $\mu$ m GaN HEMT device, quiescent condition  $V_{d0} = 25$  V and  $V_{g0} = -3$  V (dotted line),  $V_{g0} = -4$  V (continuous thin line),  $V_{g0} = -5$  V (continuous thick line). The measured load lines are superimposed to dc characteristics at  $V_{g0} = 0$  V. The crosses in the enlarged view within the inset correspond to the same instantaneous voltage pair ( $v_g = 0$  V,  $v_d = 5.4$  V).

Moreover, also the knee walkout [3], [4] can be simply characterized. In Fig. 2.4 different measurement sets are reported to characterize such a phenomenon; measurements were carried out with different drain voltage quiescent conditions and setting the amplitude of the input incident signals in order to dynamically reach the value  $v_g = 0$  V. It is well evident how the knee region is subject to a shift as the average value of the drain voltage increases.

Finally, more complex device behavior can be investigated, which can be particularly useful for discussing and defining assumptions typically adopted in the framework of nonlinear modeling. To this end a 0.25- $\mu$ m GaN HEMT device having a periphery of 150  $\mu$ m, biased under class-A operation (V<sub>g0</sub> = - 2 V, V<sub>d0</sub> = 25 V), was considered. In particular, the device was excited with very different waveform shapes, under the constraint of dynamically reaching the zero volt gate voltage value. The incident signals applied to the DUT input port are shown in terms of their spectral components (Table 1), and corresponding time-domain voltage waveforms (Fig. 2.5a).

The phase of the incident signals applied at the DUT output port have been set to achieve a 180° displacement with respect to the input signal (such a choice corresponds to a resistive-like load

#### A new approach to microwave power amplifier design

line), whereas the corresponding amplitudes were properly chosen to dynamically hit the device knee region.

Fig. 2.4: Measurements performed by exploiting the new large-signal measurement system on a 800- $\mu$ m GaN HEMT device, quiescent condition  $V_{g0} = -3$  V and  $V_{d0} = 25$  V (continuous lines),  $V_{d0} = 35$  V (dotted lines). Amplitude of the gate incident signal phasor  $A_g = 1.5$  V. Relative phase between gate and drain incident signal phasors  $\Delta \phi = 180^{\circ}$ . Different load lines are obtained by varying the amplitude of the output incident signal phasor. Measurements are superimposed to dc characteristics at  $V_{g0} = 0$  V.

| Sine | Half-sine  | Composite | Frequency |

|------|------------|-----------|-----------|

|      |            |           |           |

| 1\0° | 0.58\70°   | 0.14\-91° | 2 MHz     |

| 0    | 0.31\140°  | 0.58\127° | 4 MHz     |

| 0    | 0.08\-150° | 0.38\86°  | 6 MHz     |

Table 1: Magnitude and phase of the incident signals applied to the DUT input port

Chapter 2

Fig. 2.5: Measurements performed on a 150- $\mu$ m GaN HEMT by exploiting the proposed large-signal measurement system, quiescent condition (V<sub>g0</sub> = -2 V, V<sub>d0</sub> = 25 V). a) Time-domain voltage waveforms at the device gate port. b) Measured load lines. Three load lines are shown for the same gate voltage condition (thin, thick and dotted lines) by varying the amplitude of the output incident signal phasors. Also the dc characteristic for V<sub>g0</sub> = 0 V is shown

The corresponding load-lines, evidencing the knee walk-out, are shown in Fig. 2.5b. The crosses in the enlarged view within the inset correspond, for the different load lines, to dynamic points having the same value of the instantaneous gate voltage ( $v_g = 0$  V): it is evident that these points trace a unique dynamic characteristic. This confirms the empirical results presented in [7] and the theoretical assumption adopted in [5], [6]: when no important deviations influence the device thermal state (this is true under class-A due to the low-efficiency operation involved), the trapping state can be assumed univocally defined by the average values of the voltages applied at the device ports and no dependence is observed on the voltage waveforms.

The provided results could be indirectly obtained also by means of high-frequency time-domain measurement systems [4], [7-15]. Nevertheless two reasons make the proposed characterization technique preferable when electron device low-frequency dispersion is dealt with. The first one is that parasitic and reactive effects, under high-frequency operation, tend to hide the response of the intrinsic "algebraic" part of the device (i.e., the resistive core), and the second one is the simplicity and definitely low cost of the proposed measurement technique.

### 2.1.2 Large-signal measurements for highefficiency operation

The described setup can be exploited in order to operate as a low-frequency multi-harmonic active load-pull system: by controlling gate and drain incident signals and their relative phase, at the fundamental frequency and its harmonics, different load terminations can be arbitrary synthesized for given bias conditions. Thus, by exploiting waveform engineering approach, optimal I/V load-line satisfying the theoretical requirements associated to a selected amplifier class of operation can be experimentally searched for.

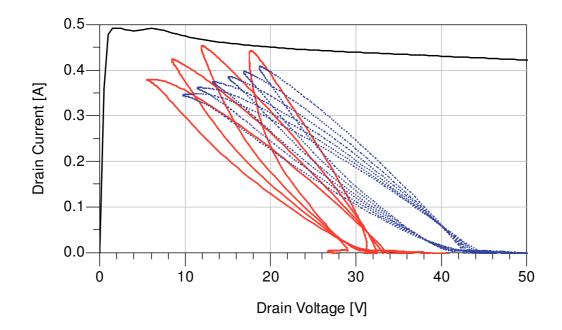

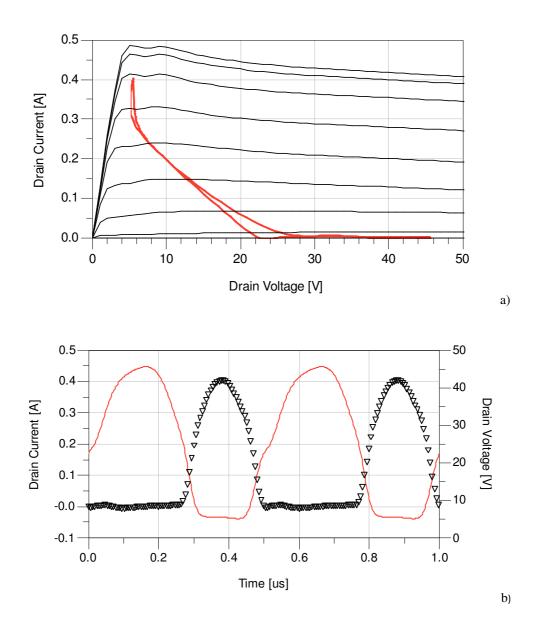

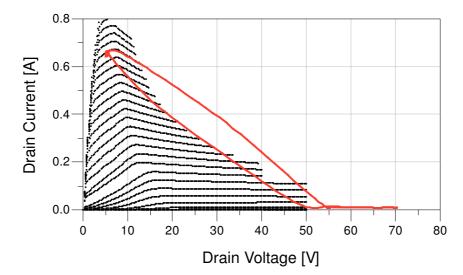

To highlight such capabilities of the described setup, large-signal measurements, oriented to high-efficiency power amplifier design [7], [16-17], were carried out on a 0.7x800  $\mu$ m<sup>2</sup> GaN HEMT. The bias condition was V<sub>g0</sub> = -4 V and V<sub>d0</sub> = 25 V (class B operation), whereas the incident signals applied at the DUT ports are summarized in Table 2 in terms of their spectral components.

| Gate Incident<br>Signal Phasors | Frequency | Drain Incident<br>Signal Phasors |

|---------------------------------|-----------|----------------------------------|

| 2\85°                           | 2 MHz     | 6.2\-107°                        |

| 0                               | 4 MHz     | 2.3\152°                         |

| 0                               | 6 MHz     | 1.3\-110°                        |

Table 2: Magnitude and phase of the RF signals applied to the DUT

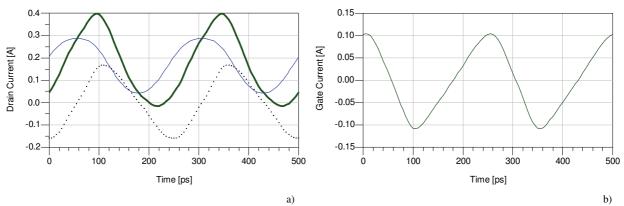

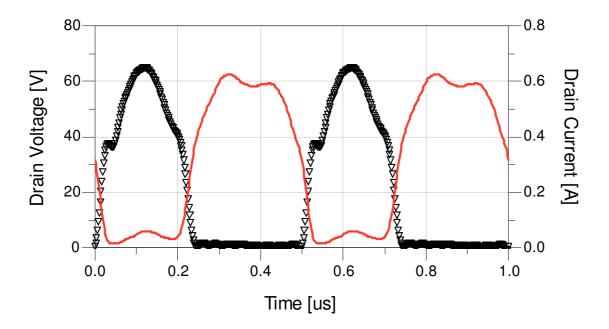

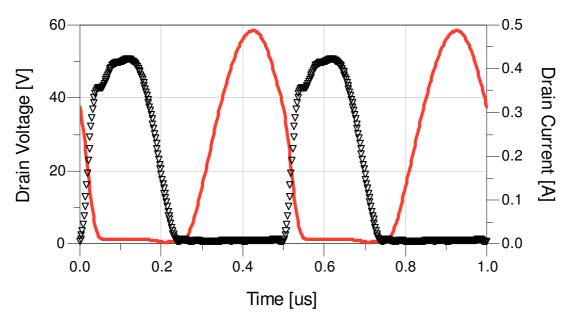

Fig. 2.6a shows the dynamic load line corresponding to the described measurement condition. It is evident that a typical high-efficiency operation is obtainable by simply controlling the amplitude and phase of the fundamental, second and third harmonic components of the incident signal at the

drain terminal of the DUT. In this particular case study, an output power of 2.2 W was measured, corresponding to a drain efficiency of 74 %.

Fig. 2.6: Measurements performed by exploiting the proposed large-signal measurement system on a 800-µm GaN HEMT device, quiescent condition ( $V_{g0} = -4 \text{ V}$ ,  $V_{d0} = 25 \text{ V}$ ). a) The measured load line is superimposed to dc characteristics ( $-4 \text{ V} \le V_{g0} \le 0 \text{ V}$ , step 0.5 V). b) Time-domain voltage (continuous line) and current (triangles) waveforms at the device drain terminal, corresponding to the synthesized high-efficiency operation.

At a few megahertz, the input port of a FET behaves as an open circuit until the off-state of the gate-source diode is preserved. This greatly simplifies the control of the gate incident signal. In the present case, a 4-V amplitude of the gate input voltage is imposed, that leads to a peak-value equal to zero volt. In Fig. 2.6a the device DC characteristics (-4 V  $\leq$  V<sub>g0</sub>  $\leq$  0 V) are shown: it is well evident that, due to the current collapse [3], the load-line is not able to dynamically reach the drain-

#### A new approach to microwave power amplifier design

current values corresponding to the dc characteristic at  $V_{g0} = 0$  V. Moreover an important knee walkout [3], [4] is present. It is evident how the proposed setup effectively characterizes the limits of the given technology.

Time-domain waveforms at the drain port of the electron device are shown in Fig. 2.6b. The dynamic current looks like an half-wave rectified sine-wave, which is different from zero where the drain voltage is minimum, according with high-efficiency power amplifier operation modes [16], [17]. In this context, the capability of synthesizing a given load-line and get information on suitable drain and gate terminations for the device resistive core, can be exploited not only for I/V modeling under realistic operation but also for amplifier design approaches, like the one that will be proposed in the next section.

It is of interest to investigate some commonly accepted assumptions related to power amplifier design. CAD-based amplifier design techniques are based on the accurate knowledge of the device intrinsic resistive core. A clear example is provided by the Cripps' load-line theory [16] which identifies the optimum device operation by analyzing the device dc characteristics and defining the optimum loading condition as the resistance that maximizes voltage and current excursions. As a matter of fact, all amplifier design techniques, from class-A to high efficiency (e.g., class F), are de facto based on the definition of the optimum waveforms of the electrical quantities at the device intrinsic current source, i.e. the device resistive core. However, due to traps and thermal effects [5-6], the transistor resistive core shows under dynamic operation a behavior which is very different with respect to the static one. The proposed setup has the unique capability of directly and exhaustively characterizing such a behavior.

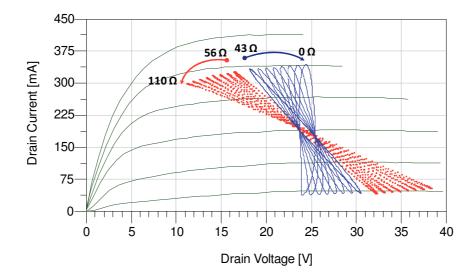

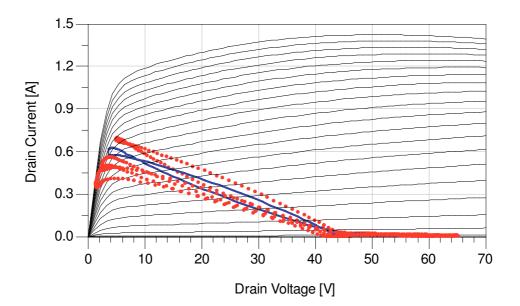

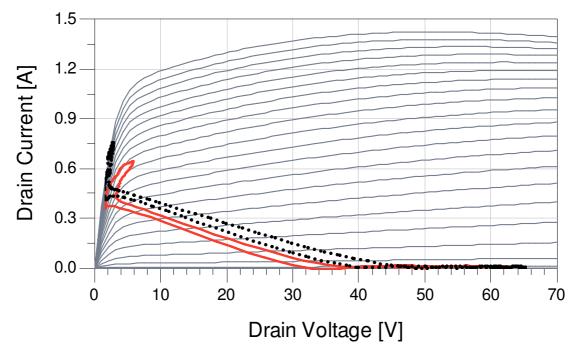

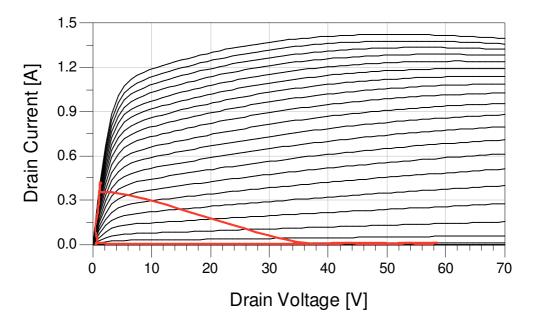

As a case study we investigate the behavior of a  $0.25 \times 400 \ \mu m^2$  GaN HEMT under highefficiency operation. In particular, Fig. 2.7 shows three different load lines providing the different performance levels reported in Table 3. Also in this case the impact of low-frequency dispersion on the device performance is well evident. The device is not able to dynamically reach the DC characteristic at  $V_{g0} = 1$  V and the I/V knee under dynamic operation is well far from the dc one. Both these phenomena, by limiting the drain current and voltage excursions, reduce the deliverable output power with respect to the one predictable on the basis of the dc characteristics.

By observing the load lines in Fig. 2.7, at a first glance it is well evident which is the best one. Efficiency and power are the worst ones for the thick load line since it involves the highest dissipation path and minimizes the drain current excursion. Similar considerations indicate that the thin load line is the best one. Such a simplicity in stating the best operating condition has to be regarded as peculiar to the proposed setup, since a similar information cannot be drawn by observing extrinsic load lines carried out at microwave frequencies.

Fig. 2.7: Different load lines synthesized by exploiting the proposed large-signal measurement system on a 400-µm GaN HEMT device, quiescent condition ( $V_{g0} = -4 \text{ V}$ ,  $V_{d0} = 30 \text{ V}$ ). Amplitude of the gate incident signal fundamental phasor  $A_g = 2.5 \text{ V}$ . Relative phase between gate and drain incident signal fundamental phasors  $\Delta \phi = 180^{\circ}$ . The measured load lines are superimposed to dc characteristics (-6 V  $\leq V_{g0} \leq 1 \text{ V}$ , step 0.5 V).

| Load Line | Output Power | Efficiency |

|-----------|--------------|------------|

|           |              |            |

| Thick     | 1.25 W       | 54 %       |

| Circles   | 1.64 W       | 60 %       |

| Thin      | 1.72 W       | 61 %       |

Table 3: Performance related to the different load lines shown in Fig. 2.7

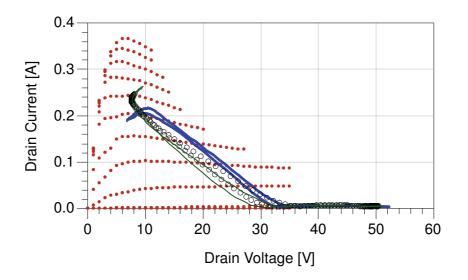

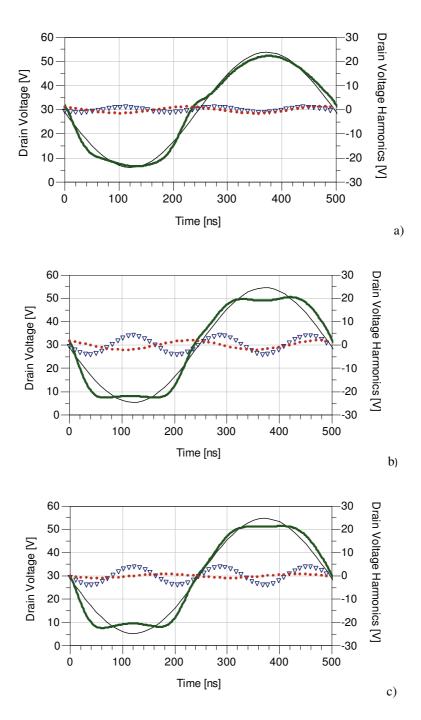

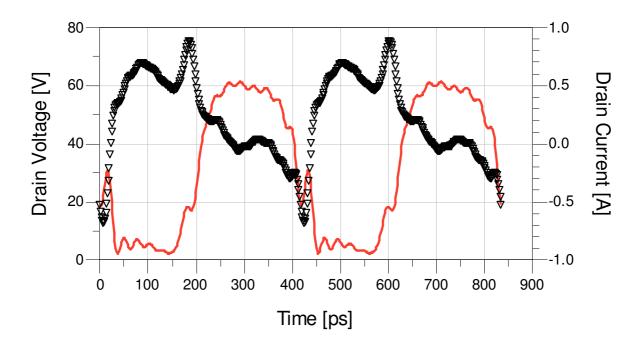

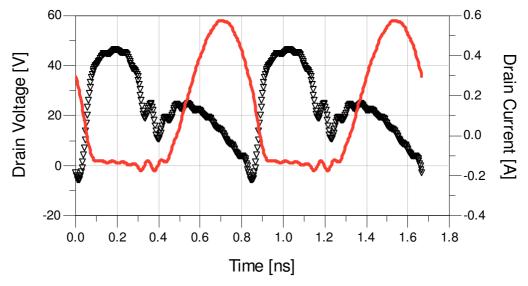

Theoretical considerations can be also carried out by observing the intrinsic drain voltage waveforms corresponding to the considered load lines; they are shown in Fig. 2.8 with their harmonic components. Fig. 2.8a refers to the thick load line, in this case only the fundamental tones of the input and output incident signals have been controlled. This is evident by looking at the second and third harmonics which assume very low amplitudes. Fig. 2.8b refers to the circles load-line, in this case the amplitude and phase of the third harmonic of the output incident signal have been manipulated also. It is evident the contribution of the third-harmonic, which, being out-of-phase with respect to the fundamental one, raises the amplifier performance according to class-F operation [17]. Nevertheless, class-F operation requires also a short loading condition at the second harmonic, this condition can be simply obtained by manipulating also the second harmonic of the output incident signal. The result is shown in Fig.2.8c, where the amplitude of the second harmonic has been halved.

Fig. 2.8: Measurements performed by exploiting the proposed large-signal measurement system on a 400- $\mu$ m GaN HEMT device, quiescent condition (V<sub>g0</sub> = -4 V, V<sub>d0</sub> = 30 V). Time-domain voltage waveform (bold line) and its harmonic components (fundamental - fine line, second harmonic – dots, and third harmonic - triangles) corresponding to the three load lines reported in Fig. 5. a) thick line, b) circles, c) thin line.

In Table 4, the load impedances synthesized for the different load lines are reported. The impedances at the 2nd and 3rd harmonics differ from 50  $\Omega$  although, for the thick load line, only the fundamental phasor of the incident signals has been exploited. This can be explained by considering that the values in Table 4 refer to the DUT planes and account for the non idealities of the measurement setup (e.g., 30-W power amplifier output impedance, attenuation and delay provided

| Load Line | Fundamental         | 2 <sup>nd</sup> Harmonic | 3 <sup>rd</sup> Harmonic |

|-----------|---------------------|--------------------------|--------------------------|

|           |                     |                          |                          |

| Thick     | 219 – i*19 Ω        | 36 + i*13 Ω              | 47 + i*20 Ω              |

| Circles   | 182 – i*11 Ω        | 37 + i*13 Ω              | 349 – i*47 Ω             |

| Thin      | $177 - i*10 \Omega$ | 1 + i*15 Ω               | 481 – i*94 Ω             |

by the signal paths). By looking at the impedance values in Table 4, it is evident how the impedances synthesized for the thin load-line are the nearest ones to the ideal class-F amplifier behavior (i.e., a short circuit at the second harmonic and an open circuit at the third harmonic).

Table 4: Synthesized load terminations for the different load lines shown in Fig. 2.7

Measurements carried out by adopting the proposed setup, besides representing a valid tool for the design of power amplifiers, may result extremely useful in the identification phase of nonlinear electron device. As a matter of fact, the operating conditions exploited in the identification phase are privileged in terms of the accuracy that the model can guarantee. As a consequence, nonlinear models extracted by adopting measurements under actual device operations unquestionably offer an higher level of accuracy.

## 2.2 The proposed design approach

The design methodology here discussed finds its motivations in electron device nonlinear modeling theory. For the sake of clarity, electron device nonlinear modeling issues, already discussed in the previous chapter, are here briefly recalled.

As shown in Fig. 2.9, in the equivalent circuit representation of a transistor, three parts can be discerned: the linear extrinsic parasitic network, that describes the access passive structure to the device active area; the capacitive core, that is responsible of electron device nonlinear dynamic effects and the resistive core, that accounts for LF I/V device behavior. These cores, representing the intrinsic device (i.e., the active area), can be considered electrically in parallel.

A new approach to microwave power amplifier design

Fig. 2.9: Nonlinear equivalent circuit for an FET Electron Device.

The aim of the design methodology is to overcome the accuracy limitations due to the complex modeling of the ED resistive core, by using a direct experimental characterization of the LF I/V load-line. To this end, the low-frequency (i.e. 2 MHz) setup described in the previous section is exploited in order to achieve active load synthesis capabilities in the framework of power amplifier design. As said, in fact, at the frequencies of few megahertz, the FET representation in Fig. 2.9 is strongly simplified since the parasitic network can be represented by means of parasitic resistances (accounting for metallization and channel access losses), while the reactive elements can be completely neglected. Therefore, the low-frequency load-line synthesized at the external terminals is practically coincident<sup>1</sup> with the load-line imposed at the resistive core of the intrinsic electron device. Since the associated electrical regime uniquely identifies [16-18] the electron device delivered power and efficiency, the described setup provides an easy way to carry out the choice of the load-line which defines given power amplifier performance. It should be pointed out that the proposed approach enables the designer to easily choose for optimal power amplifier operation modes by experimentally monitoring and engineering the waveforms at the electron device intrinsic resistive core. Moreover, reliability issues related to high-field operations [19-21], which must be considered at the intrinsic device drain-gate terminals [22], can be directly controlled.

In order to explain how the low-frequency load-line measured at the extrinsic electron device ports can be used for power amplifier design, it is convenient to express intrinsic and extrinsic voltages and currents in terms of their practically finite number M of spectral components:

<sup>&</sup>lt;sup>1</sup> For safe of accuracy, a simple de-embedding of only resistive parasitic elements is necessary to obtain the load-line imposed at the intrinsic resistive core.

$$x(t) = \sum_{k=-M}^{M} X(k\omega) e^{jk\omega t}$$

<sup>(1)</sup>

By considering for the parasitic network in Fig. 2.9 any possible topology (based on lumped or distributed elements), intrinsic and extrinsic electrical variables are conveniently related by the following equations in the frequency domain:

$$\begin{bmatrix} V_{gs}^{i}(k\omega) \\ V_{ds}^{i}(k\omega) \\ I_{g}^{i}(k\omega) \\ I_{d}^{i}(k\omega) \end{bmatrix} = \underline{H}(k\omega) \begin{bmatrix} V_{gs}^{e}(k\omega) \\ V_{ds}^{e}(k\omega) \\ I_{g}^{e}(k\omega) \\ I_{g}^{e}(k\omega) \\ I_{d}^{e}(k\omega) \end{bmatrix}, \quad k = -M, ..., M$$

$$(2)$$

where  $\underline{H}(\omega)$  is a suitable hybrid-matrix description of the linear extrinsic parasitic network.

At microwave frequencies the harmonic components of the "global" intrinsic currents are composed of the sum of the conduction<sup>2</sup> and displacement currents denoted with the superscripts R and C, respectively:

$$\begin{bmatrix} I_g^i(k\omega_{RF}) \\ I_d^i(k\omega_{RF}) \end{bmatrix} = \begin{bmatrix} I_g^{i,R}(k\omega_{RF}) + I_g^{i,C}(k\omega_{RF}) \\ I_d^{i,R}(k\omega_{RF}) + I_d^{i,C}(k\omega_{RF}) \end{bmatrix}, \ k = -M, ..., M$$

(3)

When considering the low-frequency load-line characterization carried out with sinusoidal excitations at the fundamental frequency  $\omega = \omega_{LF}$  and its harmonics, the displacement current can be totally neglected. Moreover,  $\underline{H}(\omega)$  practically becomes a real and frequency-independent matrix (which, when considering the most common case of lumped parasitic description, reduces to the series parasitic resistors). In such a case, (2) enables to directly compute, starting from the knowledge of the low-frequency harmonic components of the extrinsic voltages and currents, the intrinsic electrical variables (and, as consequence, the intrinsic load-line) at the electron device resistive core:  $V_{gs}^i(k\omega_{LF})$ ,  $V_{ds}^i(k\omega_{LF})$ ,  $I_g^{i,R}(k\omega_{LF})$ ,  $I_d^{i,R}(k\omega_{LF})$ .

<sup>&</sup>lt;sup>2</sup> Due to the frequency-independence of the conduction current its harmonic RF-components simply coincide with the LF ones, that is  $I_x^{i,R}(k\omega_{RF}) = I_x^{i,R}(k\omega_{LF})$ .

#### A new approach to microwave power amplifier design

In order to exploit the low-frequency load-line characterization for microwave power amplifier design, the extrinsic device load and source conditions must be computed, which enables the electrical regime corresponding to the chosen intrinsic load-line to be imposed at the design frequency. To this end, the displacement currents related to the electron device capacitive core must be evaluated according to the following, explicit equations:

$$\begin{bmatrix} i_{g}^{i,C}(t) \\ i_{d}^{i,C}(t) \end{bmatrix} = \begin{bmatrix} \sum_{k=-M}^{M} I_{g}^{i,C}(k\omega_{RF})e^{jk\omega_{RF}t} \\ \sum_{k=-M}^{M} I_{d}^{i,C}(k\omega_{RF})e^{jk\omega_{RF}t} \end{bmatrix} = \sum_{k=-M}^{M} jk\omega_{RF}\underline{C}(v_{gs}^{i}(t), v_{ds}^{i}(t)) \begin{bmatrix} V_{gs}^{i}(k\omega_{LF})e^{jk\omega_{RF}t} \\ V_{ds}^{i}(k\omega_{LF})e^{jk\omega_{RF}t} \end{bmatrix}, \quad (4)$$

$\omega_{RF}$  being the fundamental operating frequency of the power amplifier with

$$v_{gs}^{i}(t) = \sum_{k=-M}^{M} V_{gs}^{i}(k\omega_{LF}) e^{jk\omega_{RF}t}$$

$$v_{ds}^{i}(t) = \sum_{k=-M}^{M} V_{ds}^{i}(k\omega_{LF}) e^{jk\omega_{RF}t}.$$

(5)

As previously said, the capacitance matrix<sup>3</sup>  $\underline{C}$  in (3) can be identified on the basis of frequencyand bias-dependent S-parameter measurements. Alternatively, the capacitive core of a suitable, already available, nonlinear model can be used.

It must be outlined that when high-frequency nonquasi-static effects are not negligible, the displacement currents cannot be explicitly evaluated in terms of a capacitance matrix only as in (4), but nonlinear circuit analysis is required. To this end any frequency- or time-domain available CAD environment can be easily adopted.

Once the harmonic components of the "global" intrinsic currents have been evaluated by (3), the extrinsic electrical variables which define the load and source extrinsic regime can be computed by:

$$\begin{bmatrix} V_{gs}^{e}(k\omega_{RF}) \\ V_{ds}^{e}(k\omega_{RF}) \\ I_{g}^{e}(k\omega_{RF}) \\ I_{d}^{e}(k\omega_{RF}) \end{bmatrix} = \underline{H}^{-1}(k\omega_{RF}) \begin{bmatrix} V_{gs}^{i}(k\omega_{RF}) \\ V_{ds}^{i}(k\omega_{RF}) \\ I_{g}^{i}(k\omega_{RF}) \\ I_{d}^{i}(k\omega_{RF}) \end{bmatrix}, \quad k = -M, ..., M$$

$$(6)$$

<sup>&</sup>lt;sup>3</sup> Please note that the difference existing, given a bias condition, among the imaginary parts of the admittance parameters  $Y_{12}$  and  $Y_{21}$  (typically modeled by a transcapacitance) can be accounted for by (4) without any approximation.

and finally the load impedance at the fundamental and harmonic frequencies can be obtained:

$$Z_{L}(k\omega_{RF}) = -\frac{V_{ds}^{e}(k\omega_{RF})}{I_{d}^{e}(k\omega_{RF})}.$$

(7)

In addition, also the input device "large-signal impedance" can be easily computed:

$$Z_{IN}\left(k\omega_{RF}\right) = \frac{V_{gs}^{e}\left(k\omega_{RF}\right)}{I_{g}^{e}\left(k\omega_{RF}\right)}.$$

(8)

which, for instance, can be used to synthesize the optimum source impedance (i.e.,  $Z_s = conj(Z_{IN})$ ) which provides a matching condition under large-signal operation. It should be outlined that this information is not obtainable through scalar load-pull systems [23-25], but only by adopting a time-domain load-pull measurement setup [26-28].

To summarize, the proposed approach, which is based on low-frequency, large-signal measurements and bias/frequency-dependent small-signal measurements performed in the frequency range of interest for the considered design, is fully able to provide the same kind of information obtainable by means of expensive nonlinear measurement setups operating at microwave frequencies. The only assumption is that a negligible uncertainty can be achieved in the description of the intrinsic electron device capacitive core whose accuracy ultimately defines the frequency limitations. As will be demonstrated in the following sections, by adopting very different experimental examples, such an hypothesis is more than reasonable from a practical point of view.

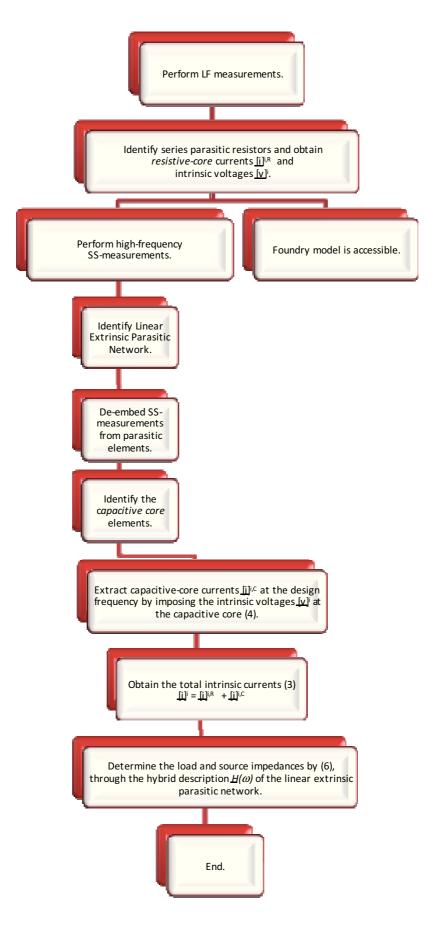

The flowchart reported in Fig. 2.10 describes the fundamental steps of the proposed design techniques.

A new approach to microwave power amplifier design

Fig. 2.10: Flowchart describing the proposed design technique.

Chapter 2

### 2.2.1 Class-A power amplifier design example

In this section, a class-A power amplifier example, operating at the central frequency of 4 GHz, is discussed. The electron device adopted for the present case of study is a C-band 0.7 x 800  $\mu$ m<sup>2</sup> GaN HEMT, whose foundry specifications are reported in Table 5.

| Quantity               | Value     |

|------------------------|-----------|

|                        |           |

| Breakdown Voltage      | 80 V      |

| Pinch-off Voltage      | -3.5 V    |

| Idss                   | 700 mA/mm |

| Saturated Output Power | 4 W/mm    |

Table 5: 0.7-µm GaN HEMT technology specifications

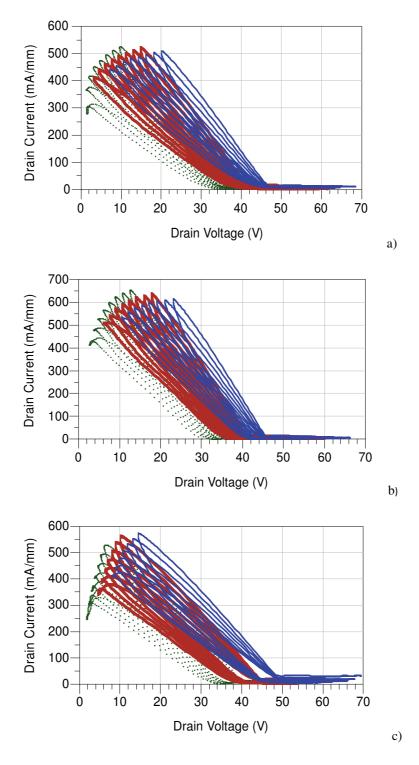

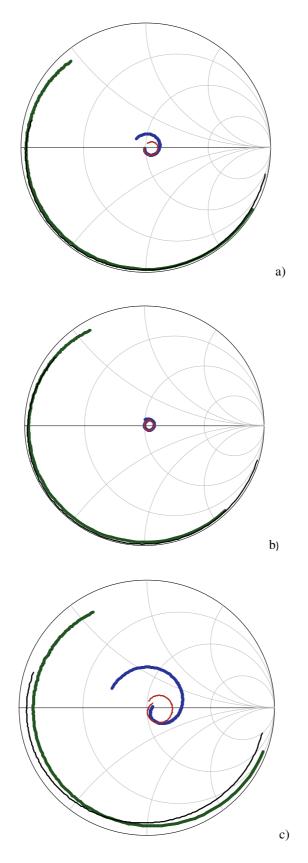

Accordingly with the design methodology described in the previous section, a preliminary low frequency characterization of the device intrinsic resistive core has been carried out: exploiting the previously mentioned active load-pull setup, the device was biased under class-A condition ( $V_{g0} = -2$  V,  $V_{d0} = 25$  V) and different load-lines were obtained by imposing a constant amplitude of the gate incident signal and sweeping the amplitude of the drain incident signal. More precisely, the amplitude of the gate incident signal was fixed at 1 V with the aim of satisfying the constraints of linear operation. Such low-frequency measurements are shown in Fig. 2.11, whereas the main experimental data for the correct choice of the intrinsic device load-line are listed in Table 6: the loading condition was chosen to meet output power and efficiency requirements, under the constraints of keeping the maximum drain-gate voltage below 42 V. As a matter of fact, the "intrinsic", low-frequency load impedance ( $Z_1 = 109.5 + i \cdot 1.3 \Omega$ ) satisfies all the design constraints.

| $Z_l [\Omega]$        | Power [W] | Efficiency [%] | $V_{dg}^{max}[V]$ |

|-----------------------|-----------|----------------|-------------------|

|                       |           |                |                   |

| $5.4 + i \cdot 5.4$   | 0.064     | 1.3            | 28.7              |

| $29.7 + i \cdot 4.3$  | 0.330     | 7.1            | 31.6              |

| 55.6 + i·2.7          | 0.585     | 12.7           | 35.3              |

| $62.5 + i \cdot 2.2$  | 0.634     | 13.9           | 36.2              |

| 76.7 + i · 1.1        | 0.736     | 16.5           | 37.9              |

| $92.4 + i \cdot 0.1$  | 0.812     | 18.5           | 39.7              |

| $109.5 + i \cdot 1.3$ | 0.881     | 20.5           | 41.4              |

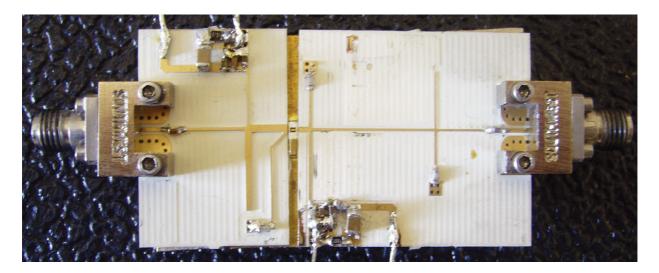

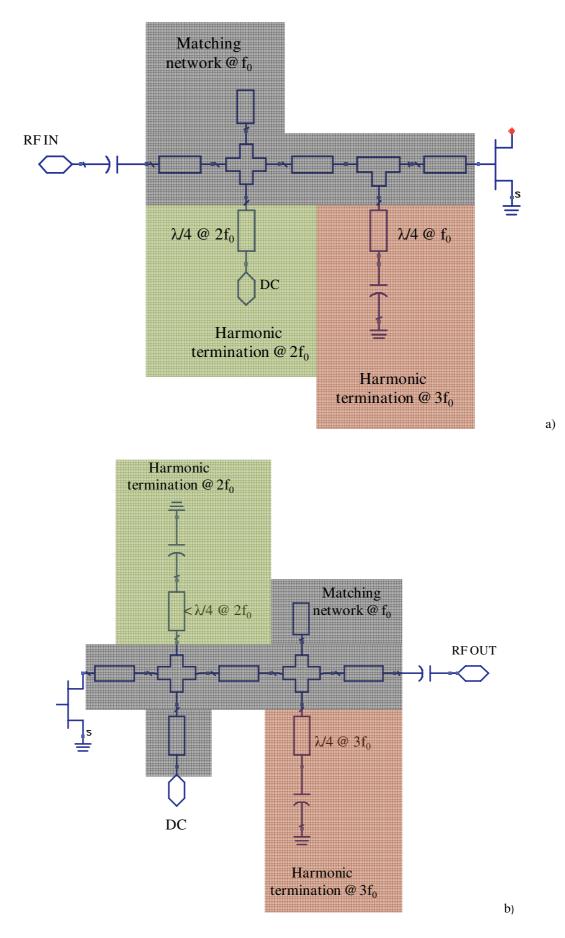

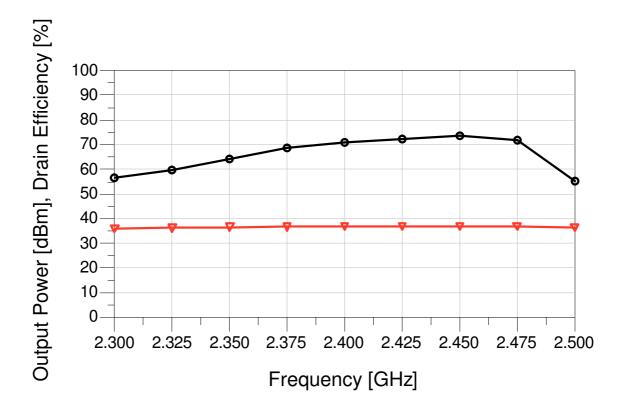

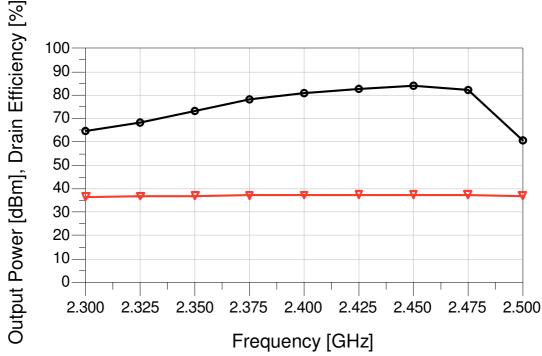

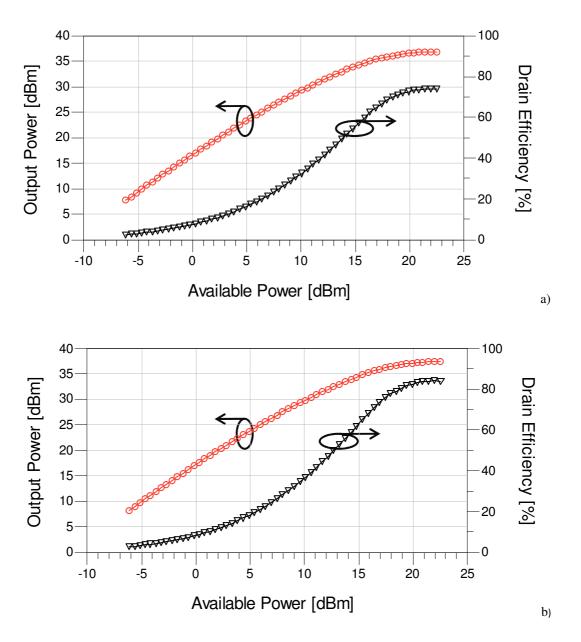

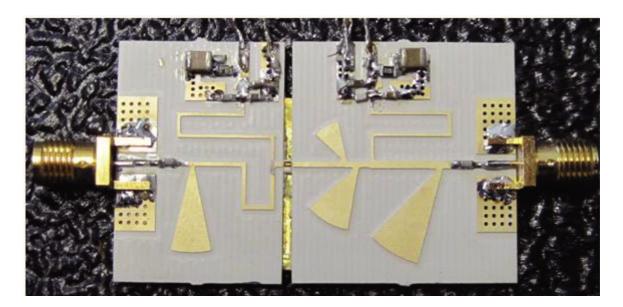

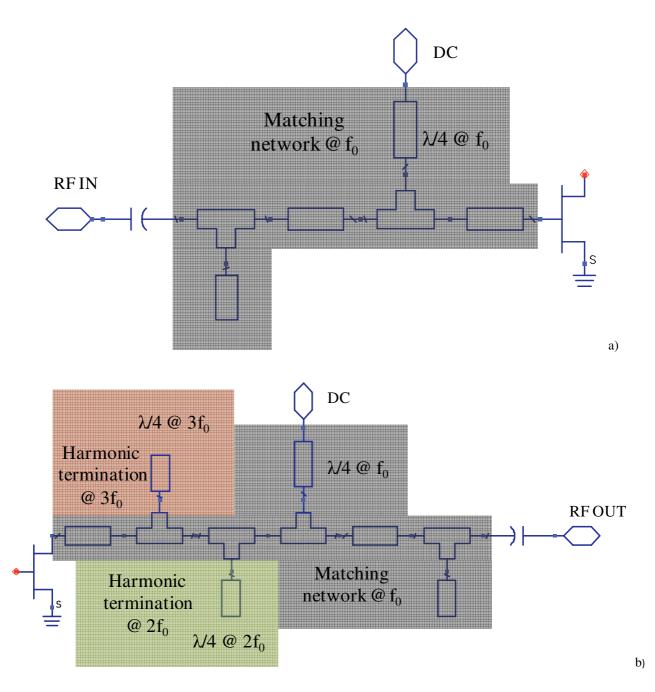

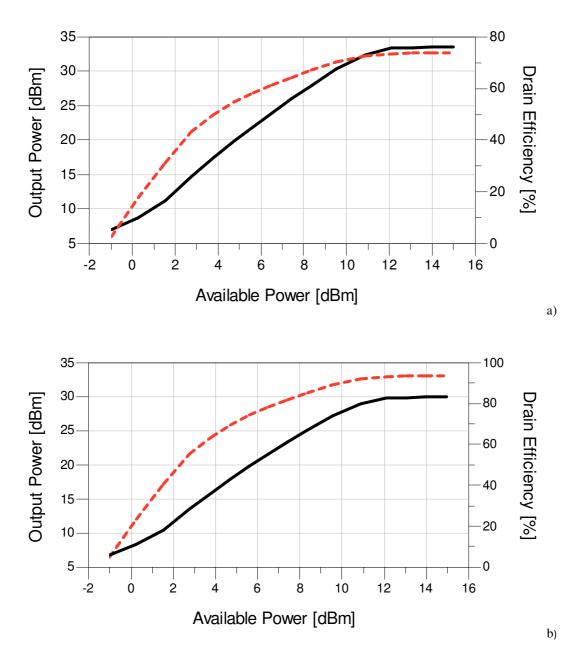

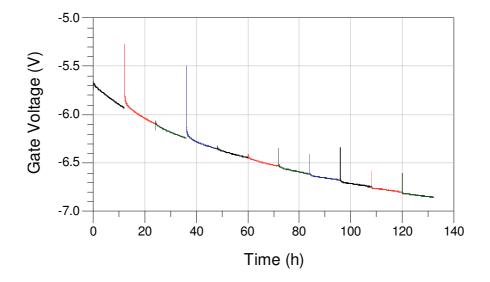

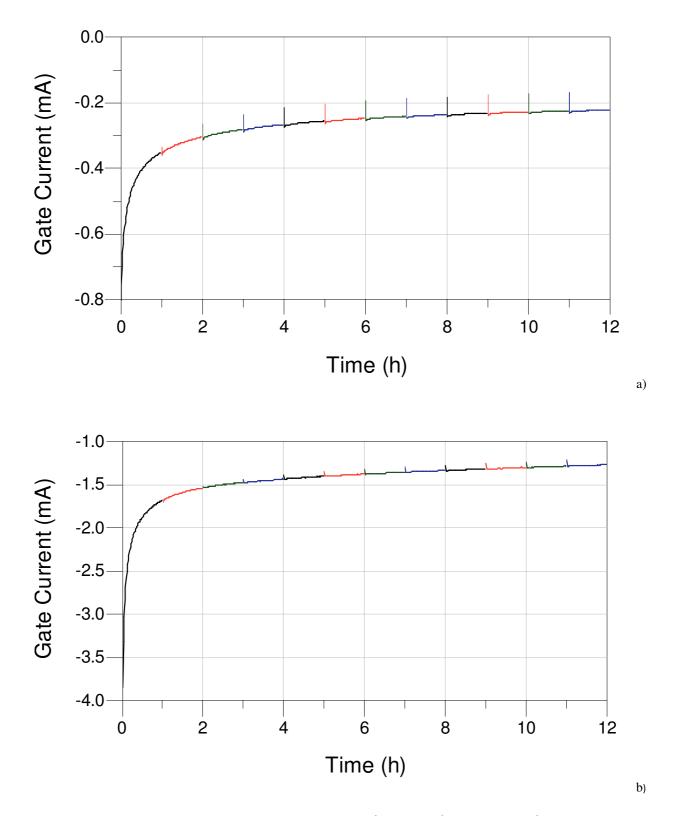

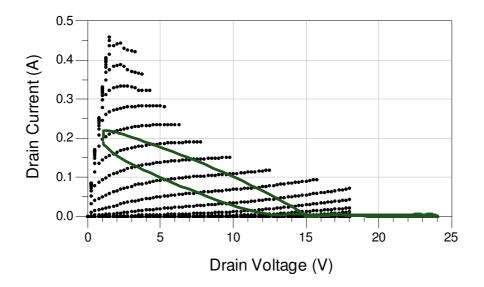

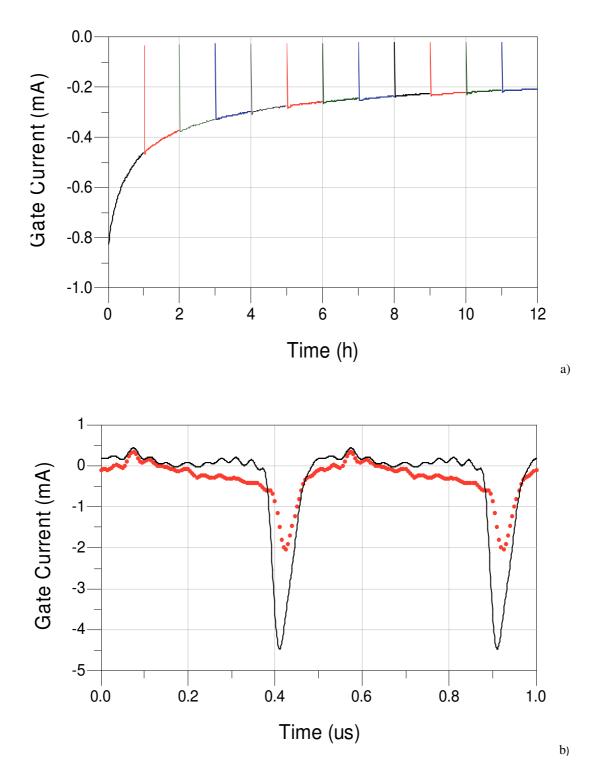

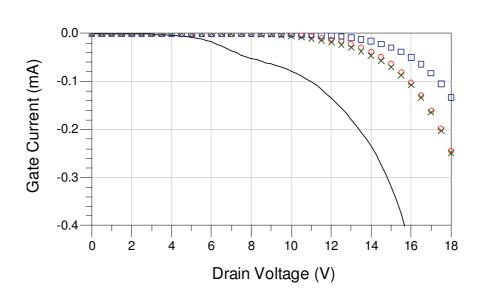

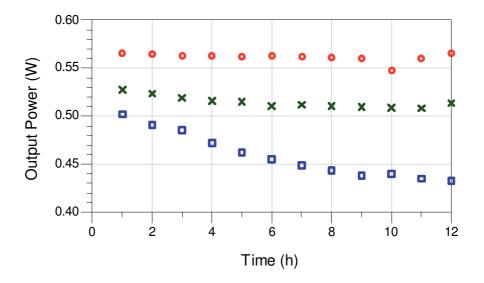

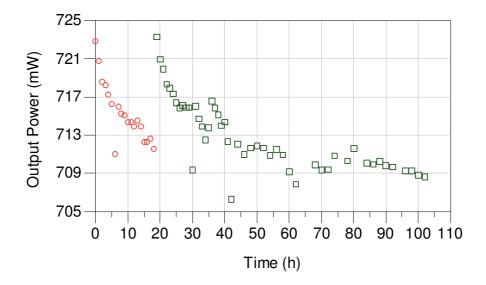

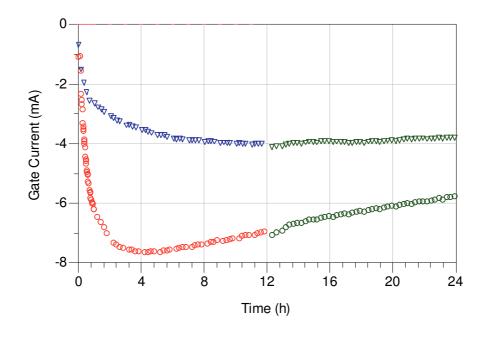

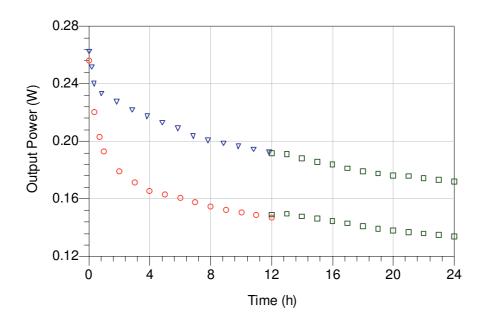

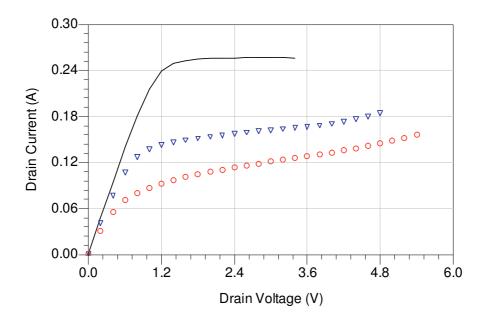

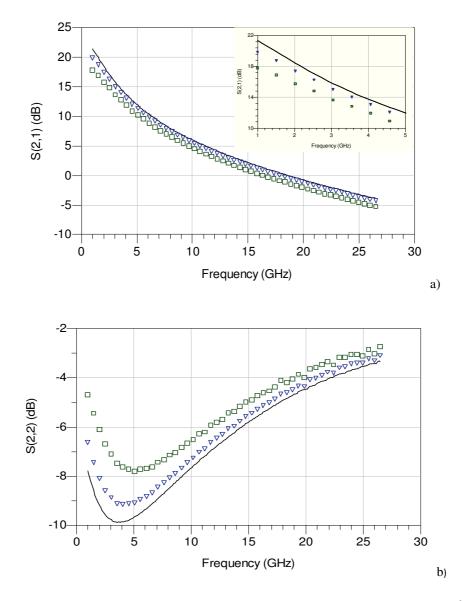

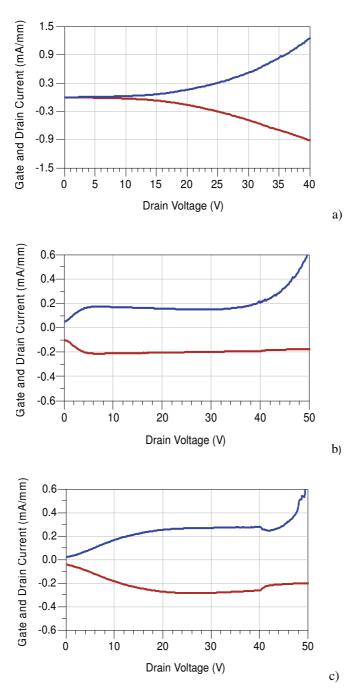

Table 6: Power, efficiency and maximum drain-voltage values obtained under lf operation as a function of the synthesized load impedances.