#### DOTTORATO DI RICERCA IN SCIENZE DELL'INGEGNERIA

CICLO XII

COORDINATORE Prof. Stefano Trillo

# A SAT based test generation method for delay fault testing of macro based circuits

Settore Scientifico Disciplinare ING-INF/05

**Dottorando**Dott. Mele Santino

**Tutore** Prof. Favalli Michele

Anni 2007/2009

## **Contents**

| C | ontei                                       | ts                                                  | i  |  |  |

|---|---------------------------------------------|-----------------------------------------------------|----|--|--|

| 1 | Inti                                        | oduction                                            | 1  |  |  |

| 2 | Digital ICs testing in macro based circuits |                                                     |    |  |  |

|   | 2.1                                         | Fault Models                                        | 6  |  |  |

|   | 2.2                                         | Automatic Test Pattern Generation (ATPG)            | 9  |  |  |

|   | 2.3                                         | Delay Fault Testing                                 | 11 |  |  |

|   |                                             | 2.3.1 Path Delay Fault Testing                      | 13 |  |  |

|   |                                             | 2.3.2 ATPG for PDF testing and Robustness           | 15 |  |  |

|   | 2.4                                         | Functional block design                             | 18 |  |  |

|   |                                             | 2.4.1 FPGA                                          | 21 |  |  |

|   |                                             | 2.4.2 Logic Bricks                                  | 23 |  |  |

| 3 | Ain                                         | of the Project                                      | 27 |  |  |

|   | 3.1                                         | Overview                                            | 28 |  |  |

|   | 3.2                                         | Review                                              | 28 |  |  |

|   | 3.3                                         | Motivation                                          | 29 |  |  |

| 4 | A n                                         | ew model for delay fault testing in macro based ICs | 33 |  |  |

|   | 4.1                                         | Signal Representation                               | 34 |  |  |

|   | 4.2                                         | PDF sensitization conditions                        | 36 |  |  |

|   |                                             | 4.2.1 Robust Conditions                             | 36 |  |  |

|   |                                             | 4.2.2 Non-Robust Conditions                         | 38 |  |  |

|   |                                             | 4.2.3 Quality of non-robust tests                   | 40 |  |  |

|   |                                             | 4.2.4 Functional sensitization                      | 41 |  |  |

ii CONTENTS

|               | 4.3                  | Accounting for Hazards                             | 42 |

|---------------|----------------------|----------------------------------------------------|----|

|               |                      | 4.3.1 Hazards on side inputs                       | 42 |

|               |                      | 4.3.2 Evaluation of hazards within the circuit     | 44 |

|               | 4.4                  | Instance of fault model                            | 46 |

| 5             | Imp                  | olementation of our approach                       | 51 |

|               | 5.1                  | Instruments                                        | 51 |

|               |                      | 5.1.1 Boolean Differences                          | 51 |

|               | 5.2                  | BDDs                                               | 52 |

|               |                      | 5.2.1 Colorado University Decision Diagram package | 54 |

|               | 5.3                  | Boolean Satisfiability                             | 55 |

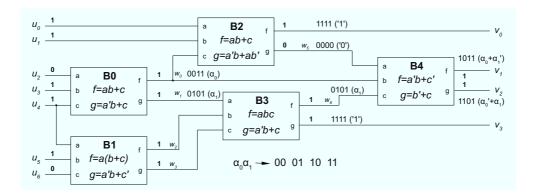

|               | 5.4                  | Test generation algorithm                          | 56 |

|               |                      | 5.4.1 Implementation                               | 58 |

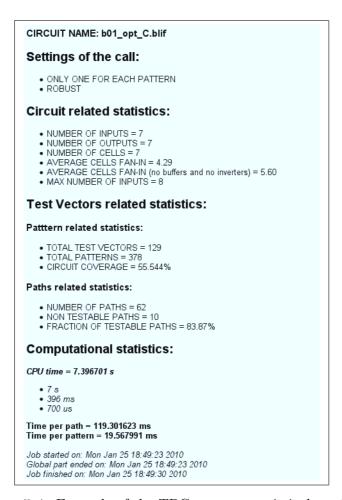

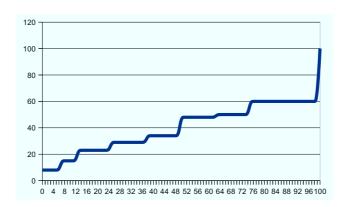

| 6             | Exp                  | perimental Measurements                            | 63 |

|               | 6.1                  | Results                                            | 64 |

| 7             | Con                  | nclusions and future works                         | 67 |

| Bi            | bliog                | graphy                                             | 71 |

| $\mathbf{A}$  | HQ                   | testing for macro-based circuits                   | 81 |

|               | A.1                  | Introduction                                       | 81 |

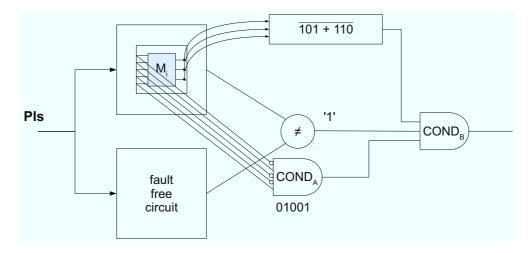

|               | A.2                  | Fault modeling and simulation                      | 84 |

|               |                      | A.2.1 Fault simulation algorithm                   | 86 |

|               |                      | A.2.2 Coverage metrics                             | 88 |

|               | A.3                  | Test generation                                    | 89 |

|               | A.4                  | Results                                            | 89 |

| Li            | st of                | Symbols and Abbreviations                          | 93 |

| $\mathbf{Li}$ | st of                | Figures                                            | 95 |

| Li            | st of                | Tables                                             | 97 |

|               |                      |                                                    |    |

| In            | $\operatorname{dex}$ |                                                    | 99 |

#### Chapter 1

#### Introduction

The main activities performed during the tree years of my PhD are related to the timing failures problems in module-based CMOS VLSI circuits.

The attention to module-based (or block-based) circuits follows the current VLSI physical design trends that attempt to limit the parametric failures due to the scaling of technology toward nanometric feature sizes. In such technologies, in fact, the traditional design paradigms that are based on small (i.e gate level) cells may produce high levels of variability, thus resulting in parametric defects. The use of highly regular cell structures, called *logic bricks* has been proposed to solve these problems thus increasing the yield of VLSI circuits. A brick comprises a logic function created from a small set of logic primitives that are mapped on to a micro-regular fabric. Such logic function is typically more complex that those implemented in traditional VLSI libraries.

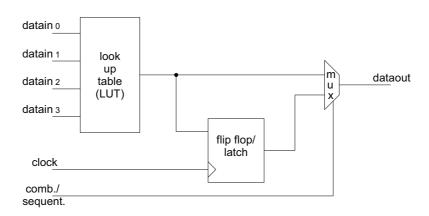

Field Programmable Gate Array (FPGA) technology also exploits a module based design approach. Unlike logic bricks, FPGAs are completely programmable, because they are based on look up tables (a n-bit LUT can accomplish every n-bit function), but the drawback is related to the implementation of the LUT, that is unknown to designer and not optimized for regularity.

In this scenario, the delay fault testing became a big issue, since it is very difficult to study a circuit built using modules whose implementation in not known, either for technological and for intellectual property reasons. Moreover, the aggressive construction technologies and the high speed of clocks make the need for delay fault testing more relevant.

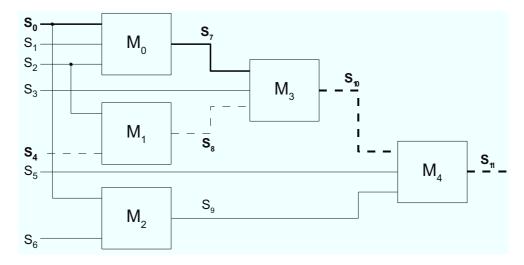

The main PhD activity, that will be explained in detail in this thesis work, is related to a new method that we propose to generate test vectors for path delay faults in circuits based on modules. Such method exploits a functional approach at module level and a structural one at circuit level.

In particular, we consider *single path delay fault testing* in a combinational circuit or in an (enhanced) full-scan one that is composed of functional blocks whose implementation is not known. We identified suitable conditions so that a test pair is able to propagate a transition through the path under test, in order to detect a path delay fault. Also, additional conditions to prevent invalidation of tests by hazards have been identified. We suppose that the dynamic behavior of the block is modeled using input delays such as in the *timing arc delay model*.

We target simple combinational blocks such as logic bricks, that are expected to present up to 8-10 inputs and a low logic depth. The used method is scalable, to generate conditions for path delay fault tests also at gate level.

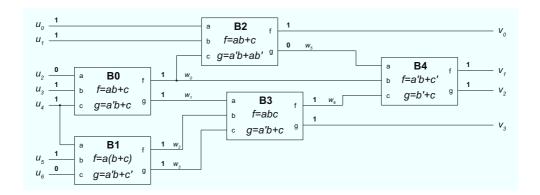

In order to assess the feasibility of the proposed approach, I realized a software, written in C/C++, that permits to find out robust and non-robust test pairs, starting from the BLIF description of a module based circuit. Such a software uses a BDD description of the blocks' functions on which we apply Boolean Differences to obtain local sensitization conditions at module level. Since there are circuits whose BDD structure may be very large and it may be inefficient (in some cases also infeasible) to treat it, we translate functions obtained at macros level to a CNF description. After that, a SAT solver generates the test pairs at circuit level starting from the conjunction of all the CNF functions.

The software tool was used to verify the proposed approach on a set of benchmarks (both combinational or full-scan) from ITC'99 and ISCAS'85 sets. Such benchmarks allowed to show the feasibility of the proposed approach, although they are not fully representative of the target circuits for which the method was developed.

Another significant work, carried out during my PhD period, also deal with testing of macro-based circuits, but it concerns specifically *logic bricks*. In particular, a method for high quality *functional fault simulation and test generation* for such circuits was conceived and a software tool that

implements it was developed.

For both the approaches, results showed the feasibility of them, but also highlighted several possibilities to improve and extend the work done. This thesis is organized in the following way: in section 2 a presentation of main digital ICs testing issues involved in this work is provided, specially whom related to macro-based circuits. In section 3 the motivation and the aims of the work is presented, while the conceptual model is discussed in more detail in section 4, followed by a round-up of the mathematical and technical instruments used to model it, in section 5. Presentation and discussion of the results, obtained from experimental measurements, are given in section 6. Conclusive remarks and future works are presented in 7.

Finally, in appendix A high quality functional fault simulation and test generation method for logic bricks will be presented.

#### Chapter 2

# Digital ICs testing in macro based circuits

Several kinds of tests are performed on a digital device during its life cycle, depending on the life phase of the circuit, on the specific application of the circuit and on others economical issues. In general, the entity that performs the different types of tests also varies.

When a new circuit is designed and realized, it needs a verification of the design and the test procedures; this is the *verification testing* and aims to validate the correct functioning of the circuit. Verification testing is performed generally with a big involvement of the chip designers.

After this phase, the chip goes in the production phase, when it needs to be checked mainly for manufacturing defects; the set of such tests is called manufacturing testing.

Finally, the chip is tested by the customer (often a systems manufacturer), that execute the so called *acceptance testing*, or *incoming inspection*.

It is possible to identify two big classes of tests [10], parametric and functional.

Parametric Testing. These tests verify if the values of AC and DC characteristics of the circuit are within the operational range. Examples of DC parameters that can be tested are: output current and voltage level, leakage current, threshold levels and input/output impedance; the AC parameters can be: propagation delay, setup and hold time,

bandwidth and noise. Since these test are related to circuit's characteristics, they are generally technology-dependent.

Functional Testing. These tests aim to verify if the circuit is able to accomplish the function for which it was designed. They are performed stimulating the circuit with input vectors and checking if the values of outputs or internal nodes are correct. This work deals with these types of tests, in particular with the generation of the test vectors for path delay faults.

#### 2.1 Fault Models

As stated above, the functional test of a combinatorial circuit consists of the sensitization of the circuit by a test vector and the subsequent check of the circuit's nodes logic values. Such nodes can be internal or can be the outputs of the logic net. Since it is impossible to generate test patterns for real defects, abstracts models of defects are needed.

A fault model is a representation of a circuit's defect (or class of defects) behavior. The fault model is necessary to the test pattern generation process and to the output response check. As stated in [62] a good fault model should satisfy two criteria: (1) it should accurately reflect the behavior of defects, and (2) it should be computationally efficient in terms of fault simulation and test pattern generation.

Although several categorization concerning fault models have been proposed, in this paragraph only a brief list of the most known models will be given, while a focus will be posed on delay fault models, later in this chapter.

Stuck-at faults. This model represents faults that have substantially three properties:

- 1. the fault site can be any node of the circuit (both an *input* or an output of a gate)

- 2. the faulty line is permanently set to  $\theta$  or 1

- 3. if only one line can be faulty it is called single stuck-at model, else it is called multiple stuck-at model.

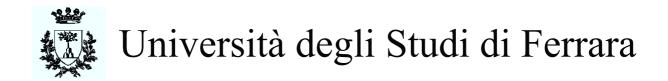

A schematic representation of stuck-at faults is shown in figure 2.1.

Figure 2.1: Examples of stuck-at faults

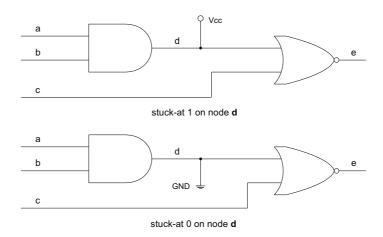

**Transistor faults.** These are CMOS device faults models; they are divided in:

- *stuck-open faults*; they represent a broken line in a transistor and can drive to a sequential behavior of the gate

- *stuck-short faults*; they represent a short between two lines in a transistor and can drive to an anomalous power consumption in steady state.

Schematic examples are shown in figure 2.5.

Figure 2.2: Examples of transistor faults

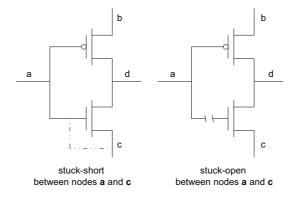

Bridging faults. These models identify a low resistance path between two nodes of the circuit; they are modeled by inserting a short (a 0  $\Omega$  resistance) between the nodes. They take different names depending on which kind of nodes are bridged together. A bridging fault can arise between:

- two terminal of a transistor; this category falls in that of transistor faults

- two nodes of a gate; this category is divided again depending upon the presence of a feedback path originated from the bridging fault.

Schematic examples are shown in figure 2.3.

Figure 2.3: Examples of bridging faults

Delay faults. They model faults that change the timing of a circuit (or a part of it) without changing its functionality. A delay fault can arise when there is an extra delay on a gate, interconnection, or memory element of the circuit. So, when the circuit is tested with a slow clock, it works properly, while testing it with at-speed clock, it may fail, because the circuit timing constraints have been violated.

Later in this chapter, the delay fault model will be discussed in more detail, with particular regard to the path delay fault model, since it will be exploited in this work.

#### 2.2 Automatic Test Pattern Generation (ATPG)

As seen before, the aim of the testing is to identify faulty circuits; to do so it is necessary to feed the circuit under test with a certain number of *test patterns*, that are input vectors capable to sensitize and find out a specific class of faults.

Since VLSI circuits are growing in dimension and density, an exhaustive test (i.e., a complete check of all the possible sites of faults under all the possible sensitization conditions) is infeasible. So an automated and sophisticated system to find test patterns efficiently is required. This task is called *Automatic Test Pattern Generation*.

Test pattern generation is a computationally complex problem, and is a central question in testing, because of the relevant theoretical concerns related to the algorithm development, but also for the implication in the circuits design. To develop an ATPG algorithm, a list of faults to be revealed is required; this list can be derived from the circuit description and a list of fault models.

The target in the ATPG algorithm development is to have an high computational efficiency and an high test vectors quality. The computational efficiency is composed of two parts, the efficiency in test generation phase and during the application of the test vectors to the circuit (in general this latter component is proportional to the number of the test vectors to apply). The quality of the test vectors is evaluated in terms of fault coverage, that is the percentage of detected faults on the total number of faults, and in terms of defect coverage, that is the amount of fault models that the algorithm can detect.

The efficiency of ATPG algorithms varies a lot, depending on the fault model considered (and its abstraction level), the type of circuit under test, and the required test quality. In brief, the purpose of a good ATPG algorithm is to individuate a (possibly) small set of vectors with the (possibly) higher coverage for the considered set of faults, in the smallest amount of time possible.

It must be noted that the goal to find a little set of vectors can be, except for small circuits, often infeasible, due to the high computational cost, but during the *fault simulation*, a compaction of test vector is generally carried out.

Although there are automatic test pattern generation algorithms for both sequential and combinatorial circuits, the generation of test patterns for sequential circuits is more difficult as several vectors are required both to activate and to propagate a fault, because also the state of the circuit must be taken into account.

There are several methods proposed in literature to address the ATPG for sequential circuits. Some of those aim to bring the sequential circuit to a combinatorial description, using specific techniques.

When it is impossible to have a combinatorial-like situation, there are approaches that extend combinatorial algorithms to the sequential condition (e.g. building sequences of the circuit's combinatorial part). Others techniques use a functional description of the circuit, to work on a state machine of the circuit.

There are design techniques that aim to enhance the testing capability of the circuit. Design of circuits using some of such techniques is called Design For Testability (DFT). In particular the scan techniques, between others things, permit to treat a sequential circuit as a combinatorial one, from the point of view of testing. In fact, since the flip-flops delays can be always included in the combinatorial part of the circuit, then it is often possible to study every combinatorial stage as a single combinatorial circuit, from the point of view of delay faults.

Combinatorial ATPGs are divided in two big categories, listed above.

Pseudo random. These techniques generate random test patterns; when a predefined coverage value is reached, the algorithm is stopped.

**Deterministic.** These techniques generate test patterns starting from the logic conditions that permit the detection of faults. There are several algorithms falling in this category; a class of them bases the test pattern search on the structure of the circuit; the most known ones are D-Algorithm [46], PODEM [25] and FAN [23]. There are also algorithms basing the search on the function of the circuit, i.e. independently from the topological information; this is the case of boolean differences-based approaches, as described in [32].

#### 2.3 Delay Fault Testing

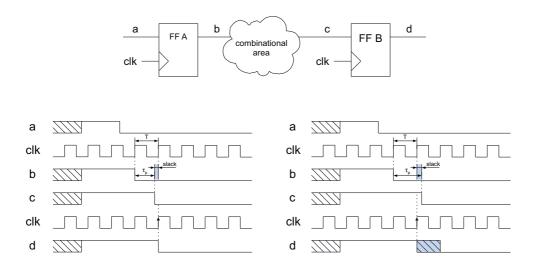

In order to obtain fault free operations in *synchronous sequential circuits*, a signal have to propagate its logic value correctly within a specified time (the clock period) along a path between two memory elements. If the signal propagation time exceeds the clock period, then a delay fault occur. A generic sequential circuit can be viewed schematically as shown in figure 2.4, that is a certain number of combinatorial areas between registering stages (composed by flip-flops or latches).

Figure 2.4: Scheme of a sequential circuit

Delay fault testing consists of propagating a transition through a block of combinatorial logic and checking if the resulting transition arrives within a predefined amount of time.

The example in figure 2.5 shows the propagation of a transition trough a combinational stages. Two possible scenarios are shown; in the first, the propagation delay is shorter than the clock period, while in the second, the combinatorial delay exceeds the time budget. The effect is that the flip flop B sample a wrong value on output c.

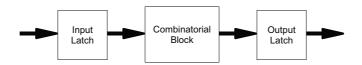

Unlike the logic faults, delay faults need two test vectors (a test pair) to be checked, the first one to propagate the initialization value (often given with a slower clock) and the second at speed, to verify if the outputs change their values before the clock event occur. The scheme used to obtain this, is illustrated in figure 2.6, where a combinatorial block is fed by a latch to load input values while another latch stores output values.

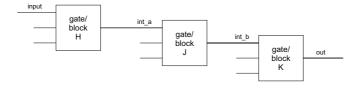

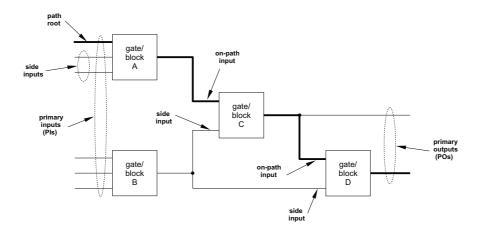

DF Models. Before to present the principal delay fault models, some terminology remarks must be given.

A path is a route between a primary input (PI) and a primary output (PO) of a circuit. A path can be represented in a schematic way as shown in figure 2.7. The primary input of a path under test is called path root, the

Figure 2.5: Propagating a transition

b)  $\tau_p > T_{clk}$

a)  $\tau_p < T_{clk}$

Figure 2.6: Delay fault testing

input on the path of a single gate/block is called *on-path input*, while the others inputs of the gates/blocks are called *side inputs*.

Figure 2.7: Schematic representation of a path

Note that the on-path input of the first gate/block of the path is the path root. Figure 2.8 shows a graphical representation of such concepts.

There are three main types of delay fault models, namely gate delay fault model, transition fault model and path delay fault model. A gate delay fault, as stated in [52], is a gate defect that results in at least one path

Figure 2.8: Path related nomenclature

fault, while a path delay fault occur when a transition applied to a path input does not arrive to the path output in time to set the output memory element. The major problem with the path delay fault model is the number of paths to be considered, in fact, in a circuit, the number of paths can became exponential in the number of gates.

The transition faults was defined in [61] by means of a slow-to-rise or a slow-to-fall fault on the output of a gate. The first models a delay defect during a rise transition, while the latter during a fall transition. If the defect on the gate is large enough to affect any path passing through it, then a transition fault exists on the specific gate.

It must be emphasized that a path delay fault is associated with an entire path, so it models a *distributed defect*, while gate delay faults and transition faults represent *local defects*; also the latter can be viewed as stuck-at faults on circuit's signals.

#### 2.3.1 Path Delay Fault Testing

"A path delay fault is a path of the combinational network between input and output latches for which a transition in the specified direction as initiated by the setting of an input latch does not arrive at the path output in time for proper setting into an output latch." [52]

A circuit path has a delay fault if the timing budget of the path is greater than the clock period; such a situation may (or may not) result in a functional error at the output(s) of the entire circuit, because of the sensitization conditions, that are not justified.

The path delay fault model considers the delay of the entire path, hence the potential delay fault is seen as distributed along the entire path. In this way, the major limitation of the others delay fault models is overcome, because the gate delay fault and the transition delay fault address local defects, while path delay fault, models global faults.

Since the path delay fault arise when the sum of the delays of the gates along the path exceed the clock interval, no matter the size of the delay of the single gate is. Also, in the path delay fault model no assumptions about the localization of the fault within the path are made, so such a model comprise also the gate delay fault model. Moreover, the amount of the exceeding time is not relevant for testing.

In order to construct a test for path delay fault in a circuit, two test vectors are required. First, the *initialization vector*, brings the circuit to the initial state using a clock with a period that allows to all signals in the circuit to stabilize (i.e., not necessarily at speed). Then the *propagation vector* activates the fault; it permits to see the fault effects on the primary outputs. The latter stage is performed using the system clock. Must be noted that, during path delay fault testing, the circuit is assumed to be fault free, obviously except for delay faults that may affect the circuit.

For every path in a circuit, up to two path delay faults can exist, one related to the propagation of the rise transition (i.e.  $0 \to 1$ ) applied to the on-path input and the other one related to the application of a fall transition (i.e.  $1 \to 0$ ) to the on-path input. Hence the maximum number of possible path delay faults in a circuit is  $2*n_{\pi}$ , where  $n_{\pi}$  is the number of paths in the circuit. In the following of this work, the association between a path and one of transitions will be referred to as pattern, so, for every path, two possible patterns can be sensitized. Note that this is true only in case of gate level circuits which does not use xor gate; in fact, as it will be observed in more depth later, xor gates or more complex functions may permit to propagate a transition both in a positive way and in a negated one.

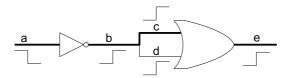

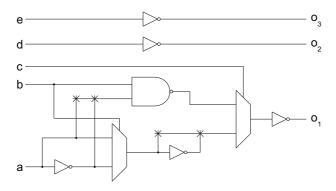

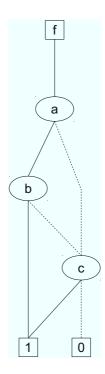

Not all the paths in a circuit can be tested for path delay faults, in fact, as shown in figure 2.9, from [62], a falling transition on path a-b-c-e can be propagated but a delay fault cannot be highlighted; paths with this

characteristic are called *statically unsensitizable*. Instead, a path that does not permit the propagation of both the transitions, is called *false path*.

Figure 2.9: A static unsensitizable but not false path

For example, in figure 2.10, the node b and the node d cannot be at high logic state (i.e. logic '1') at the same time. Thus, the path a-c-e is a false path. Note that a false path is always statically unsensitizable, but not vice versa [62], in fact, path a-b-c-e in figure 2.9 is not a false path (i.e. at least a transition can be propagated).

Figure 2.10: An example of false path

Sensitizability is the main requirement to test the paths for path delay faults, but ATPG algorithms have to find test pairs for paths with particular sensitization properties. Such properties are related to the constraints required from paths to be tested, hence are related to the test quality. These matters will be discussed in more detail in the next paragraph.

#### 2.3.2 Test Pattern Generation for Path Delay Fault Testing and Robustness

The delay fault test generation task consists in the search of the test pairs  $\langle u, v \rangle$ , such that, after applying u to the PIs of the circuit, the application of v produces a wrong output, if sampled with the test clock. ATPG for path delay fault, however, has a peculiarity, in fact test pairs can be characterized depending to the constraints needed for paths testability.

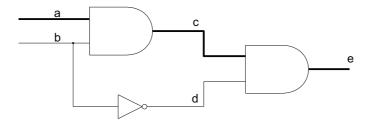

To do such a characterization, the *robustness* concept, defined in [35] is required. In [51], a possible classification of robustness classes was proposed; a schema is shown in figure 2.11, from [51]. The basic concept is that smaller is the set of path delay faults, less restrictive constraints are required and hence higher is the quality of the test pairs associated.

Figure 2.11: A classification of path delay faults

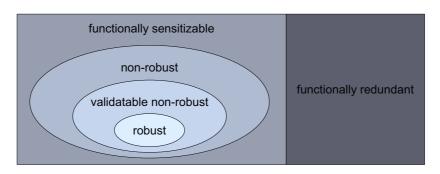

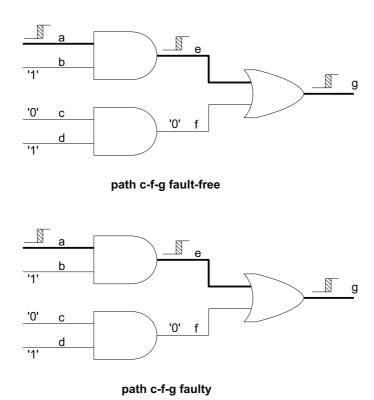

Robust Testability. If a test pair is able to find the path delay fault regardless to the presence of a delay fault in the others paths of the circuit, this test pair is a robust test. In figure 2.12 is explained a situation in which a delay on one of the off-paths can mask the detection of the delay fault of the path under test.

c=1, d=1,  $\langle a=1, b=1, c=0, d=1 \rangle$  can detect a delay fault on path a-eg, but if there is a fault on path c-f-g, it could be impossible to establish that a delay fault arise. In such a situation, the couple of vectors  $V_{nr}$  is a non-robust test for the path a-e-g.

In figure 2.13, there is an example of robust test, instead. The circuit is the same and the pattern too. In order to robustly sensitize the path a-e-g, the test pair  $V_r = \{\langle a=0, b=1, c=0, d=1 \rangle, \langle a=1, b=1, c=0, d=1 \rangle\}$  is required, in fact, as can be seen, a delay fault in path under investigation (a-e-q) is still detected, even if the path c-f-q is also affected by a path delay fault. A path that have at least one robust test is said to be robustly testable.

So, in the cited case, even if the path a-e-g has a non-robust test, it is robustly testable anyway. As can be seen in graphic representations, robust

Figure 2.12: Non-robust sensitization

testability conditions can also be viewed as the non-robust ones, with the constraint to have no hazard propagating trough the on-path.

path c-f-g faulty

Between robust and non-robust paths, there is an intermediate class of testable paths, called *validatable non-robust testable (VRN testable)* [44]. As stated above, a non-robust test can be invalidated by the presence of delay faults on certain side paths. If it is possible to ensure that such side paths are fault-free, then the non-robust test is said *validatable non-robust (VRN)* [51]. Note that the side paths may be either robustly or VRN testable themselves; in the latter case the rule is applied transitively. So, a VNR test, as a robust test, is able to detect a delay fault regardless of the presence of delay faults on side paths [51].

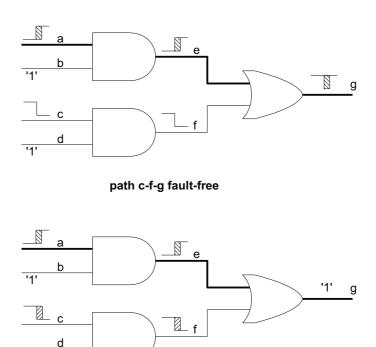

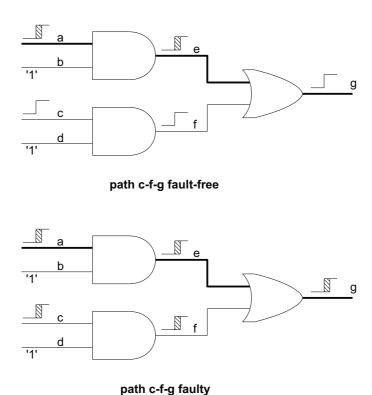

If a test is able to reveal a path delay fault only when there is another path delay fault, then such a test is called functionally sensitizable (FS). In figure 2.14 the same circuit is sensitized with the test pair  $V_{fs} = \{\langle a=0, b=1, c=0, d=1 \rangle, \langle a=1, b=1, c=1, d=1 \rangle\}$ . As can be seen, only if there is a delay fault of the path c-f-g, a delay fault on path a-e-g can be detected.

Figure 2.13: Robust sensitization

All the path delay faults that do not belong to one of the previously cited categories (i.e., are not sensitizable), are called functional redundant (FR).

In brief, a *robust* test pattern has the highest test quality (it will detect a defect no matter faulty conditions on off-input paths), the *non-robust* detects a defect if there is only a single fault on the path, and *FS* test patterns can only detect multiple defects on paths [36]. Last, *functional redundant* cannot detect any path delay fault.

#### 2.4 Functional block design

With the scaling of the CMOS feature sizes, specially toward nanoscale, and the consequent increasing of integration, the number of ways in which a chip can fail, increases. In fact, failures arise due to manufacturing defects and reliability faults, but also the impact of parametric failures is increasing.

Application specific IC (ASIC) development requires the construction of ad hoc masks for every layer; this permits to have an high grade of flexibility

Figure 2.14: Functional sensitization

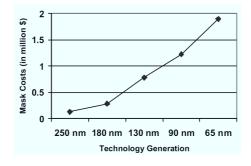

during the design, but it may became a disadvantage for the high production costs and the long time-to-market. In fact, specially with the growing of the ICs integration level and the consequent shrinking of the feature sizes, the costs for the corrective steps and silicon re-spins are greatly increased. As an example, the figure 2.15 from [65] shows the estimated trend in ASIC mask set costs.

Figure 2.15: Mask Cost vs. Technology Generation

20

The above mentioned problems with ASICs (i.e. the design costs and the high time-to-market) are driving designers to choose solutions based on more customizable devices. In particular, the trend is addressed towards configurable and programmable solutions.

There are a lot of programmable devices, but in this work the attention will be posed on Field Programmable Gate Arrays (FPGAs) and logic bricks, since these are between the most promising technologies, specially towards system on chip (SoC) paradigm and nanoscale design. The main drawback with such solutions is the loss in terms of performance, power and die area [42]; as an example, diagrams in figure 2.16 form [42] represent a comparison between FPGA and ASIC technologies.

Figure 2.16: Comparison of FPGA vs. ASIC

Field Programmable Gate Arrays can offer a valid solution to the ASICs limits, in fact they have all the advantages of programmability; besides lower design costs, thanks to the low time-to-market, they offer a further economic gain. The main drawback is the loss of efficiency, above all in terms of die area and speed.

Another possible solution to ASICs weak points could be a full-mask-set design methodology, based on *logic bricks*, an hybrid solution between standard cell ASICs and configurable arrays, proposed in [28]. As analyzed in [60], designing an IC using regular logic bricks permits to improve manufacturability, since regularity has been recognized to be a valid mean to limit the variability of circuit's parameters, that can cause malfunctioning, specially with the shrinking of ICs sizes.

#### 2.4.1 Field Programmable Gate Array

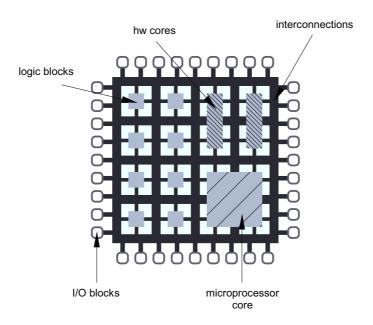

Field Programmable Gate Arrays are programmable devices constituted essentially by a matrix of programmable logic blocks (PLB), and programmable interconnections between them, connecting logic blocks between them and to programmable IOs. Over the years, several hardware cores have been added to the basic structure, such as microprocessors, DSPs (digital signal processors), blocks of RAM and FIFO (first-in first-out) memories or IP (intellectual property) cores (e.g. Ethernet mac core).

The principal characteristic of FPGAs is *programmability*. To allow programmable blocks to change their own behavior, a memory is used, the so-called *configuration memory*. Depending on the construction technology of the configuration memory, different types of FPGAs exist.

The principal classification of FPGAs is related to the programmability of the memory; in fact they can be divided in *volatile* and *non-volatile*, in *one-time programmable* and *erasable*, but they can also be *in-system programmable* or not.

Fuse technology uses bipolar transistors, while antifuse technology is CMOS-based; both are one-time programmable. EPROMs are erasable only with UV (ultra violet) light, while EEPROMs are electrically erasable, so depending from the package, they can also be in-system programmable. Better than the EEPROMs (with regard to programmability and package size), the Flash memories are erasable, but not all of them are in-system programmable. Finally SRAM-based FPGAs are in-system programmable and re-programmable, but they are non-volatile.

So, the SRAM-based FPGAs are the most versatile; for this reason, in

22

the last years, the use of such devices has grown, also because of its higher density, more features and lower costs compared to non-volatile FPGAs.

One of the major problem with SRAM-based FPGAs is that, unlike the non-volatile ones, they lose configuration when powered off, so an external memory is required to store the configuration information.

The configuration is performed by loading a stream of bits, called *bit-stream* in the configuration memory. After the boot of the device, an internal state machine configures all the programmable blocks, depending upon the information held by bitstream.

Figure 2.17 shows a schematic representation of the structure of an FPGA with a microprocessor and some hardware cores.

Figure 2.17: An FPGA schematic representation

FPGA Testing. In order to perform tests on FPGAs, the structure of such devices must be taken into account. In fact, as mentioned above, there are several kind of structures in a typical FPGA.

Testing of SRAM-based FPGAs has recently been a subject of several research studies. As stated in [30], there are two possible kinds of testing techniques for in-system reconfigurable FPGAs, external testing techniques, and those employing built-in self test (BIST) approaches.

Also, it is possible to identify testing techniques for FPGAs as application independent testing or application dependent testing [30]. The former stimulate all the FPGA parts with no regards to the task that the device will perform (i.e., the application), while the latter tests the specific configuration loaded by the user. So, application dependent testing is less general then application independent one, but it is considerably better with respect to delay faults, and in particular with path delay fault.

The advantage of application dependent testing results from the structure of the FPGAs interconnections. FPGA interconnections are *hierarchical*, that is: various matrix of interconnections exist, both global and locals, that permit to route the signals between different zones of the device. With the miniaturization trend in the manufacturing technology of FPGAs, the interconnection delay within a path can became the major contribution to the total path delay. Because it is very difficult to test all the possible interconnections during the application independent testing, doing the test for only the configured ones is more feasible.

#### 2.4.2 Logic Bricks

One of the newest approach to increase yield of the VLSI circuits construction is based on the use of highly regular structures called *logic bricks*.

"A *brick* comprise a logic function created from a small set of logic primitives that are mapped onto a micro-regular fabric" [28].

The new design methodology studied in [28], is based on a library of macro components, that must be built following two main directives. The set of primitives must be:

- 1. flexible enough to realize the logic required

- 2. small enough to limit the geometric shape within the bricks.

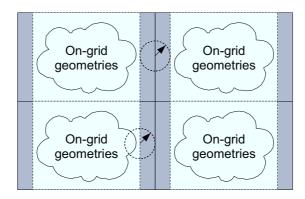

Logic bricks have been conceived to improve manufacturability of the circuits [28], because they are constructed following some rules to obtain the maximum regularity, e.g. all wires on a given layer are unidirectional, have fixed pitch, and are wide enough to avoid notches and landing pads. Figure 2.18, from [28] shows an example of these constraints.

As explained in [58], bricks layout is created in two phases consisting of transistor placement and routing. Transistor placement is performed

**Figure 2.18:** Regular Bricks. Micro-regularity constraints within bricks and compatible borders (shown in gray) provide macro-regularity compatible over radius of influence

using an extended branch-and-bound technique that minimizes wire length and cell area, both of which are estimated during brick creation. *Routing* for a logic brick is accomplished by transforming the problem to a SAT formulation.

In figure 2.19, from [28], an example brick is showed. As can be seen, the number of points that can be programmed (marked with a X) is very low, compared with the full-customizable FPGA basic block, shown in figure 2.20. In fact the latter use a n-bit look up table (LUT) that can accomplish every n-bit function; the drawback is related to the implementation of the LUT, that is unknown to designer and not optimized for regularity and area occupation.

Figure 2.19: Example of a logic brick

Figure 2.20: Schema of a FPGA basic block

#### Chapter 3

### Aim of the Project

Delay fault testing and at-speed testing are widely used to verify the timing of synchronous digital IC's. The importance of these techniques is still growing because of the relevant IC's parameters uncertainties which characterize the current technologies [5, 6, 11].

In order to drive this process, several fault models and test generation techniques have been developed that target different trade-offs between accuracy and efficiency.

The largest fraction of these approaches is based upon gate level descriptions of the circuit [51]. In case the basic building blocks are more complex than logic gates and their implementation is not known, functional level approaches have been proposed [43, 64]. For instance, this is the case for look-up tables based Field Programmable Gate Arrays (FPGAs) and it may be a perspective for deep submicron circuits that exploit logic bricks as basic building blocks [28]. This class of circuits has been referred to as macro [43] or module based [64].

The path delay fault model [52] can be used in both gate and macro based combinational (full-scan) circuits to detect distributed defects resulting in timing violations. Path delay fault testing verifies the timing of paths by providing sensitization conditions ensuring that errors are produced when transitions are propagated through paths whose delays exceed their timing budget.

#### 3.1 Overview

Robust testing [35] is the main paradigm ensuring the verification of a path's timing independently from the timing of other paths in the circuit. This goal is typically achieved by preventing from the propagation of *hazards* along the path under test.

In this regards, the specific case of module/macro based circuits, however, presents two main differences with respect to the gate level case.

The first one depends on the possibly complex internal structure of macros which, differently from simple CMOS gates, may contain different internal paths that let a transition on a specific input to propagate to a macro's output. For this reason, there are delay fault models that, if the macro implementation is not known, conservatively assume that every input configuration sensitizing a path from the macro's input to its output is characterized by an independent value of delay to be verified in the testing phase [43, 64].

The second difference regards the problem of hazard generation that, in macro based circuits, is more complex than in gate based ones. In gate level circuits, in fact, a hazard can be generated only because of skews between the arrival times of suitable transitions of at least two gate inputs (function hazard) [39]. In the case of macro based circuits, reconverging paths within the macro may generate an output hazard even if only a single input switches (logic hazard).

#### 3.2 Review

In this section, a brief review of the works strictly related to the activity presented in this thesis and that partially stimulate the interest in such matters, will be given.

In [43], a functional delay fault model has been developed for combinational circuits containing macros. In such a work, function robust path delay faults have been defined to describe the conditions for the robust propagation of a transition through a macro. These conditions are computed by using a signal representation that relates a triple to each signal denoting:

1. the value to which the signal eventually stabilizes when applying the

3.3. MOTIVATION

first test vector;

- 2. the value during the transition;

- 3. the value to which the signal stabilizes after the application of the second test vector.

29

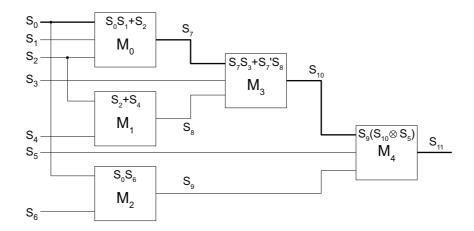

Robust conditions are then computed by analyzing the truth table of the macro. These conditions are computed for each macro along a path and the path delay fault is considered to be tested by a set of test pairs justifying all the possible combinations of robust conditions. This kind of approach will be thereafter referred to as exhaustive path verification.

In [64], a delay fault test generation method for modular circuits is presented. Such a method exploits the ease of boolean expressions manipulation that is provided by ordered binary decision diagrams (BDDs) [8]. In order to reduce the occurrence of logic hazards, the robust sensitization conditions used in this method are more restrictive than in [43]. Because of this, the robust conditions described in [64] do not scales down to gate level conditions when modules implementing simple elementary logic functions are considered. Also, this method considers exhaustive conditions for robust path delay fault testing. In addition, the authors provide a technique for the design of hazard-free logic modules ensuring that the proposed test generation method detects all robustly testable paths in gate level implementation of modules.

#### 3.3 Motivation

The methods proposed in the literature mainly focus on robust tests which ensure high levels of test quality. However, when robust tests are not available, non-robustly sensitizable paths and even functionally sensitizable paths [51] may result in timing violations and should be verified by delay fault testing.

In this regards, during my PhD period, a new method for delay fault testing of circuits based on modules that allows to account for robust, non-robust and functional sensitization conditions was proposed. This approach can support any kind of delay fault model including the exhaustive conditions considered in [43] and [64]. However, the approach was specifically

applied to the case of small combinational modules whose timing can be reasonably modeled using the *timing arc delay model* [17]. The use of such an approximate model is justified by the growing relevance of interconnect delays in submicron digital ICs [27] and by the relevant sources of timing defects that may affect such interconnects such as those due to breaks or opens [12, 3, 34].

Our method is based on a *signal representation* that allows to describe path delay fault testing constraints.

For each on-path macro, the proposed method uses boolean differential calculus supported by the BDD package described in [53] to compute different kinds of side input sensitization conditions. Robust, non-robust and functional sensitization conditions are expressed as a function of the macro's input signals.

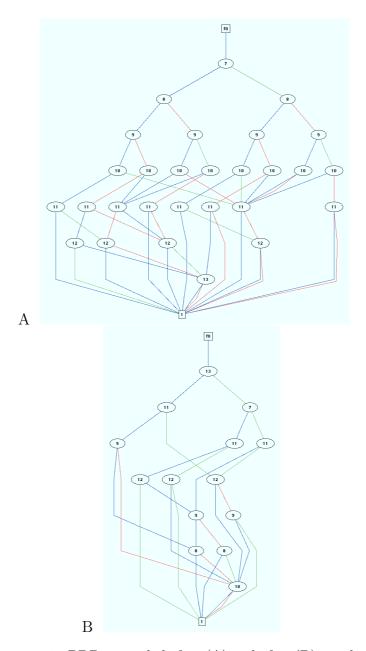

The set of test pairs detecting the considered path delay fault can be computed by expressing the sensitization conditions of all the macros along the path as a function of the variables describing the values of PIs and by performing the conjunction of such functions [64]. This approach may be expensive for some class of circuits that cannot be efficiently described in terms of ordered BDDs [9].

To approach this problem, an alternate technique based on boolean satisfiability [1] was used. This kind of technique has been successfully applied to delay fault test generation both in *combinational* [13] and *sequential* [20] *ICs*.

In a first step, the proposed approach uses BDDs and boolean differences to compute the different kinds of sensitization conditions for each on-path macro as a function of macro's input signals. Then it translates these functions to *conjunctive normal forms* (CNFs). The constraints on the side inputs of on-path macros are justified by using additional CNFs that describe the consistent operations of each macro in the circuit with the initialization and the launch test vector. An additional CNF describing the (function) hazard generation and propagation is also computed for each macro in the circuit.

Finally, the CNF that describes the whole set of test pairs detecting the considered path delay fault is computed as the conjunction of all the above mentioned CNFs. If existing, a test pair for the considered path delay fault can be found by invoking a *SAT solver* [40] on such a final CNF.

The SAT approach to test pairs generation becomes attractive when searching for only a subset of all the possible test vectors; in fact, for circuits that can be efficiently managed using BDDs, the methods completely based on BDDs [64] are expected to be more effective in evaluating all the possible test vectors than the proposed one.

The proposed approach is here instantiated by considering an example of fault model that well matches with the case of small combinational macros. Such a model has been suggested in [30] to the purpose of FPGA testing. It supposes that the propagation delay from an input to the output of a macro depends only on the kind (rise/fall) of input and output transitions. Therefore, the fault is considered to be tested when all the possible consistent combinations of rising and falling transition of on-path signals have been verified. Each of them will be referred to as a pattern of the considered path. The CNFs describing the kind of signal transitions for a specific pattern can be simply added to the CNF describing sensitization conditions and circuit's operations. If existing, a test pair detecting such a fault can be found by invoking any SAT solver (zChaff [40] is used in this instance).

Within the considered delay model, the proposed approach allows for a correct management of function hazards. In case of more complex circuits, the timing arc approximation becomes not realistic and the generation of internal logic hazards cannot be neglected.

Finally, it must be noted that the proposed *signal representation* allows to describe the problem of robust and non-robust test generation as pseudo boolean [1] optimization problem.

The feasibility of the proposed approach has been verified by applying it to a set of macro based combinational benchmarks that has been obtained by modifying the ISCAS'85 [7] benchmarks and the full-scan, synthesized version of some of the ITC'99 benchmarks [16].

# Chapter 4

# A new model for delay fault testing in macro based ICs

This work addresses single path delay faults in a combinational circuit or in an (enhanced) full-scan [18] one, that is composed of *functional macros* whose implementation is not known.

As stated before, when testing for a path delay fault, two test vectors  $\langle u, v \rangle$  are applied to the circuit, allowing a transition to propagate through the faulty path; these vectors constitute a test pair and are called initialization and launch (or propagation) test vectors respectively. The initialization vector u is applied at a low test rate, thus ensuring that each line of the circuit has enough time to reach its steady state value. Then, the propagation test vector v is launched and the circuit outputs are captured using a fast test rate. The time elapsing between the launch of v and the capture of POs signals is the clock period T; for the sake of simplicity, timing parameters of flip-flops are not considered.

In order to detect a path delay fault (i.e. a path delay exceeding the timing constraints), the used test pair has to propagate a transition through the path under test. This kind of test may be invalidated by hazards, so, to prevent from this kind of problems, suitable conditions have been identified [51].

As explained in section 2, the robust testing paradigm ensures that a path delay fault, that makes the path's delay larger than T, is detected

by a robust test independently of any other delay inside the circuit. This definition has been initially introduced in the case of gate level networks in [35], and in [43] it has been extended to circuits composed of functional macros.

The macros along the path implement functions  $f : \mathbb{B}^n \to \mathbb{B}$  ( $\mathbb{B} = \{0, 1\}$ ) and the dynamic behavior of the single block is modeled using input delays such as in the timing arc delay model [17]. Such a model is widely used in timing analysis, but, differently from timing analysis, these delays are not quantified in path delay fault model, that considers them as unbounded.

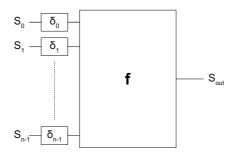

This timing model, illustrated in figure 4.1, is not well suited for complex combinational blocks, because it misses both the possibly different paths within a block and the possible paths' recombination between blocks, giving rise to the generation of logic hazards.

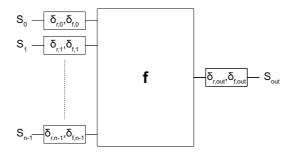

Figure 4.1: Simple timed model of a functional block (macro)

This work target simple combinational macros, such as logic bricks, that are expected to present up to 8-10 inputs and a low logic depth. In such modules, the generated logic hazards should present a reduced width, thus being easily filtered out by the logic in their transitive fan-out.

#### 4.1 Signal Representation

In order to characterize the sensitization conditions of macro's side inputs, the following signal representation is used.

Let  $u_i$  and  $v_i$  be the final  $(t \to \infty)$  values of a signal  $s_i$  belonging to a path p when u and v are applied to the circuit, respectively.

In particular, let  $t_0$  and  $t_0 + T$  be the instants triggering the launch of v and the capture of the corresponding POs, respectively. Let also  $\delta_i$  be the

actual slack of  $s_i$  with respect to the path's end when the considered test pair is applied. Depending on the path's side inputs, the logic value sampled at path's end may be sensitive to the value  $w_i$  of  $s_i$  at  $t_{s_i} = t_0 + T - \delta_i$  (this value will be referred to as the *sampled* value of  $s_i$ ). A logic error may be sampled if  $w_i \neq v_i$ .

In order to characterize signals from the point of view of the sampled value (an unbounded delay model is used), a boolean variable  $(\alpha_i)$  is related to each signal. In particular,  $\alpha_i = 0$  denotes the case where  $w_i = v_i$  while  $\alpha_i = 1$  denotes the case where a delay fault may make  $w_i \neq v_i$ . Now, the case of hazards is not considered and therefore, when  $\alpha_i = 1$ ,  $w_i = u_i$ . In a hazard-free and single path context,  $\alpha_i$  characterizes the timing behavior of  $s_i$  with the current test pair.

Using  $\alpha_i$ , the value of a signal  $s_i$  under the possible presence of a delay fault is characterized by:

$$w_i = (\alpha_i u_i + \alpha_i' v_i). \tag{4.1}$$

Note that  $\alpha_i$  is not referred to a particular defect location, but to the timing of the whole path.

Considering b, a single output combinational block, described under the simplified timing arc delay fault model in figure 4.1 (this model will be refined in section 4.4),  $S_b = (s_0, s_1, \ldots, s_{n-1})$  is the ordered set of the input signals of a block and  $f_b : \mathbb{B}^n \to \mathbb{B}$  is the implemented function. If  $U_b = (u_0, u_1, u_2, \ldots, u_{n-1})$  and  $V_b = (v_0, v_1, v_2, \ldots, v_{n-1})$  are the ordered sets of variables denoting the values of signals belonging to S when the test vectors u and v are applied, respectively, then the correct value sampled at the block output signal  $(s_{out})$  is  $v_{out} = f_b(v_0, v_1, v_2, \ldots, v_{n-1})$ .

Finally, let  $\alpha_b = (\alpha_0, \alpha_1, \dots, \alpha_{n-1})$  be the ordered set of the variables determining the value of  $w_i$  for each input of the block.

If the sampled values of the input signals of b are denoted as  $W_b = (w_0, w_1, w_2, \dots, w_{n-1})$ , then, in the actual circuit, the following relationship holds:  $w_{out} = f_b(w_0, w_1, w_2, \dots, w_{n-1})$ .

For instance, in case  $f_b = v_0 v_1 + v_2$ , sampled values are given by:

$$w_{out} = (\alpha_0 u_0 + \alpha'_0 v_0)(\alpha_1 u_1 + \alpha'_1 v_1) + (\alpha_2 u_2 + \alpha'_2 v_2) =$$

$$= \alpha'_0 \alpha'_1 v_0 v_1 + \alpha'_0 \alpha_1 v_0 u_1 + \alpha_0 \alpha'_1 u_0 v_1 + \alpha_0 \alpha_1 u_0 u_1 + \alpha_2 u_2 + \alpha'_2 v_2$$

It must be noted that the proposed signal representation is equivalent to the one proposed in [43]. The use of the variables  $\alpha_i$  is here introduced to explicitly denote delay fault effects and to enable the use of boolean differential calculus.

# 4.2 Path Delay Fault testing sensitization conditions

In case a transition is propagated through a path containing the block b with output out, a logic error is sampled at the path's end if:

$$\sigma_b = w_{out} \oplus v_{out} = 1. \tag{4.2}$$

$\sigma_b$  describes all the configurations of  $U_b$ ,  $V_b$  and  $\alpha_b$  that produce the sampling of a wrong logic value at the path's end in case the value of  $s_{out}$  is propagated through a sensitized path.

In the particular case of single path delay faults, the condition that  $s_k \in S_b$  is the on-path input require that a path delay fault is on the path  $(\alpha_k = 1 \text{ and a logic error is sampled at path end } (\sigma_b = 1)$ , so the following relationship can be imposed:

$$\sigma_{b,k} = \sigma_b \alpha_k = 1.$$

The kind of transition propagated to  $s_k$  can be imposed as the conjunction of  $\sigma_{b,k}$  with the suitable values of  $u_k$  and  $v_k$ . For instance, a rising transition can be described as  $u'_k v_k$ , thus leading to the following condition:

$$\sigma_{b,k}^{rise} = \alpha_k u_k' v_k \sigma_b = 1, \tag{4.3}$$

that describes all the possible kind of sensitization conditions for the side inputs of the considered block (robust, non-robust and functional) in case of a rising transition of  $s_k$ . As it will be shown, the kind of sensitization conditions depends on the values to be assigned to the variables  $\alpha$  of the off-paths to satisfy equation 4.3.

#### 4.2.1 Robust Conditions

The possible values of the side inputs that ensure *robust test conditions* for the considered block need to be computed. This test paradigm is simply

enforced by making fault detection independent of any delay in the circuit other than that of the tested path. In this case, it can be simply imposed that  $\sigma_{b,k}$  must be independent of the values of  $\alpha_j$ ,  $\forall j \neq k$ . This condition  $(\rho_{b,k})$  can be expressed in closed form using the *boolean differences* with respect to all the possible non-empty subsets of  $\alpha_{b,k} = \alpha_b \setminus \{\alpha_k\}$ . In particular, it is:

$$\rho_{b,k} = \left(\sum_{\substack{j \neq k \ j=0}}^{n-1} \frac{\partial \sigma_{b,k}}{\partial \alpha_j} + \sum_{\substack{i \neq k \ j=i+1}}^{n-2} \sum_{\substack{j \neq k \ j=i+1}}^{n-1} \frac{\partial^2 \sigma_{b,k}}{\partial \alpha_i \partial \alpha_j} + \sum_{\substack{i \neq k \ j=i+1}}^{n-3} \sum_{\substack{j \neq k \ j=i+1}}^{n-2} \sum_{\substack{l \neq k \ j=i+1}}^{n-1} \frac{\partial^3 \sigma_{b,k}}{\partial \alpha_i \partial \alpha_j \partial \alpha_l} + \dots \right)$$

$$\cdots + \frac{\partial^n \sigma_{b,k}}{\partial \alpha_0 \dots \partial \alpha_{k-1} \partial \alpha_{k+1} \dots \partial \alpha_{n-1}}$$

$$(4.4)$$

where  $\partial f/\partial x$  is the boolean difference of f with respect to x ( $\partial f/\partial x = f|_{x=0} \oplus f|_{x=1}$ ).

In the remainder of this work, the disjunction of all the boolean differences of the generic function g with respect to all non-empty subsets of boolean variables in the generic set A will be denoted to as  $\mathcal{D}(g, A)$ . Therefore, equation 4.4 can be rewritten as:

$$\rho_{b,k} = \mathcal{D}(\sigma_{b,k}, \alpha_{b,k})'. \tag{4.5}$$

The set of input configurations of the logic block must satisfy both the condition of error detection in case of path delay fault on the on-path  $(\sigma_{b,k})$  and the robust propagation conditions (given by  $\rho_{b,k}$ ). So the relationship holds:

$$\eta_{b,k} = \rho_{b,k}\sigma_{b,k} = 1. \tag{4.6}$$

$\eta_{b,k}$  includes all the possible robust sensitization conditions (that are independent of the variables in  $\alpha_{b,k}$  set) for the on path input  $s_k$ . Note that these conditions allow for transitions on side inputs. This may increase the logic hazards probability, but it allows to explore cases related to multiple input transitions that may have an impact on the timing of CMOS ICs [14, 55].

It is worth mentioning that the closed form formulation of  $\rho_{b,k}$  involves the computation of  $2^{n-1}-1$  coefficients. As an alternative, the dependencies on  $\alpha_i$  can also be eliminated in an iterative or recursive way:

$$\eta_{b,k}^{i} = \begin{cases} \sigma_{b,k} & \text{if } i = -1\\ \eta_{b,k}^{i-1} \left(\frac{\partial \eta_{b,k}^{i-1}}{\partial \alpha_{i}}\right)' & \text{if } 0 \leq i \leq n-1 \ \land \ i \neq k \end{cases}$$

(4.7)

requiring a linear number of computations. The final value of  $\eta_{b,k}$  can be computed as:

$$\eta_{b,k} = \begin{cases} \eta_{b,k}^{n-1} & \text{if } k \neq n-1\\ \eta_{b,k}^{n-2} & \text{if } k = n-1. \end{cases}$$

(4.8)

In the example introduced in section 4.1, if  $s_0$  is the on-path input, conditions are:

$$\eta_{b,0} = u'_0.v_0.v_1.u'_2.v'_2 + u_0.v'_0.u_1.v_1.v'_2.$$

In this expression, the two product terms correspond to the cases of rising and falling transitions of  $s_0$ , respectively. The corresponding pairs of input vectors are shown in table 4.1.

These assignments to the block's side inputs provide *robust conditions* for fault effect propagation, avoiding the possible generation of *functional hazards* at the output of the block. Conversely, they do not provide any protection with respect to *logic hazards* generated inside the block, because the method herein described does not consider blocks' internal implementation.

It must be noted that, in case  $f_b$  corresponds to the function of a logic gate, the presented method provides the traditional conditions for robust test generation.

#### 4.2.2 Non-Robust Conditions

The problem of *non-robust tests* in circuits composed of combinational macros has not yet been addressed in details in the literature. However, in case no robust test exists for a given path, it may still give rise to timing errors and it should be tested. To this purpose, non-robust side input assignments that are not included in the robust set are also addressed in this work. So, it is required that:

- a) at least one side input has a fault-free delay (thus violating robustness);

- b) no side input should be required to be delayed (the violation of this condition would lead to functional sensitization).

For a given pair of macro's input values  $(\langle u, v \rangle)$ , condition a) can be expressed as:

$$\exists j \neq k : \sigma_{b,k}(u,v)|_{\alpha_i=1}=0$$

while condition b) is:

$$\neg \exists j \neq k : \sigma_{b,k}(u,v)|_{\alpha_j=0} = 0.$$

The conjunction of these conditions  $(\mu_{b,k})$  can be expressed in a more compact way as:

$$\mu_{b,k} = \sigma_{b,k} \big|_{\prod_{j \neq k} \alpha'_j} \cdot \left( \sigma_{b,k} \big|_{\prod_{j \neq k} \alpha_j} \right)' = 1 \tag{4.9}$$

where  $\sigma_{b,k}|_{\prod_{j\neq k}\alpha'_j}$  represent the evaluation of  $\sigma_{b,k}$  when  $\alpha_j = 0 \ \forall j \neq k$  (i.e. the generalized cofactor of  $\sigma_{b,k}$  with respect to  $\prod_{j\neq k}\alpha'_j$ ) and  $\sigma_{b,k}|_{\prod_{j\neq k}\alpha_j}$  is the evaluation of  $\mu_{b,k}$  when  $\alpha_j = 1 \ \forall j \neq k$ .

The set of input test pairs satisfying both the condition of error sampling (with error on the on-path)  $(\sigma_{b,k})$  and non-robust minus robust condition  $(\eta_{b,k})$  are given by:

$$\theta_{b,k} = \sigma_{b,k}\mu_{b,k} = 1. \tag{4.10}$$

So,  $\theta_{b,k}$  groups those test pairs that do not satisfy robust constraints while they still ensure non-robust sensitization conditions.

Therefore, once robust test generation for a given path delay fault fails, non-robust test sequences may be generated.

In the example of section 4.1, it is:

$$\theta_{b,0} = u_0' v_0 v_1 u_2 v_2' \alpha_2' + u_0 v_0' u_1' v_1 u_2' v_2' \alpha_1'.$$

As can be seen, the first product term corresponds to a rising transition of  $u_0$  and defines a set of configurations of U and V that detects the fault only if  $\alpha_2 = 0$ . The second product term describes a test set detecting the fault only if  $\alpha_1 = 0$ . The corresponding test vectors are shown in table 4.1.

The whole set of non-robust tests can be computed as:

$$\xi_{b,k} = \eta_{b,k} + \theta_{b,k} = 1. \tag{4.11}$$

As an alternative,  $\xi_{b,k}$  can be directly computed by using the following formulation that, for each side input, imposes that either the test is independent of the considered side input timing or it requires that it has a

| kind of sensitization   | $\mathbf{u_0}\mathbf{u_1}\mathbf{u_2}$ | $\mathbf{v_0}\mathbf{v_1}\mathbf{v_2}$ | $lpha_0lpha_1lpha_2$ |

|-------------------------|----------------------------------------|----------------------------------------|----------------------|

| robust                  | 0-0                                    | 110                                    | 1                    |

|                         | 11-                                    | 010                                    | 1                    |

| non-robust minus robust | 0-1                                    | 110                                    | 1-0                  |

|                         | 10-                                    | 010                                    | 10-                  |

**Table 4.1:** Robust and non-robust test conditions for the block implementing the function ab + c

fault-free timing:

$$\xi_{b,k}^{i} = \begin{cases} \sigma_{b,k} & \text{if } i = -1\\ \xi_{b,k}^{i-1} \left( \alpha_i' + \left( \frac{\partial \xi_{b,k}^{i-1}}{\partial \alpha_i} \right)' \right) & \text{if } 0 \le i \le n-1 \ \land \ i \ne k \end{cases}$$

$$\xi_{b,k}^{i-1} \qquad \text{if } i = k$$

$$(4.12)$$

requiring the computation of a linear number of coefficients. The values of  $\xi_{b,k}$  can be computed as:

$$\xi_{b,k} = \begin{cases} \xi_{b,k}^{n-1} & \text{if } k \neq n-1\\ \xi_{b,k}^{n-2} & \text{if } k = n-1 \end{cases}$$

(4.13)

#### 4.2.3 Quality of non-robust tests

In the case of non-robust tests, the number and the timing of the side inputs which do not satisfy robust constraints have a strong impact on the probability that a non-robust test is invalidated in spite of a path delay larger than the available slack [49, 15]. In particular, non-robust tests featuring the longest path segments which are robustly testable are preferable to others, as shown in [49]. Also, side inputs that do not satisfy robust test constraints should stabilize to their final value as soon as possible, as shown in [15].

Since the presented method makes use of the unbounded delay hypothesis, the only way to improve the *quality* of non-robust tests is to minimize the number of side inputs that do not satisfy robust constraints.

From this point of view, equation 4.11 does not pose any constraints on the quality of non-robust tests, which will depend on random choices performed by SAT solver. However, the problem can be approached by using a pseudo boolean formulation.

As known, pseudo boolean solvers [1] can minimize linear functions in the form  $\sum_i a_i b_i$  where  $a_i \in N$  and  $b_i \in \{0, 1\}$ , according to boolean constraints that are typically expressed as CNFs. This property can be exploited in order to minimize the number of side inputs that do not satisfy robust constraints.

In case a solution of equation 4.11 requires a fault-free transition of a side input  $s_i$ , the corresponding variable  $\alpha_i$  is set to 0. Conversely, if this constraint is not present,  $\alpha_i$  may be set to any value. Therefore, if  $\mathcal{Q}$  is the set including all the side inputs of blocks along the path, the cost function to be minimized is:

$$\Psi = \sum_{\forall i \in \mathcal{O}} (1 - \alpha_i)$$

where the sum is the arithmetic one.

In case the solver achieves  $\Psi = 0$ , a robust test is found, otherwise, the minimization process will reduce the number of side inputs that do not satisfy robust constraints, thus providing a high quality non-robust test. This formulation of the high quality path delay fault testing as a pseudo boolean problem may take advantage from any performance improvement of pseudo boolean solvers.

#### 4.2.4 Functional sensitization

The test pairs that satisfy equation 4.2 (i.e. the fault sampling conditions) but does not satisfy non-robust conditions are referred to provide only *functional sensitization* conditions [51] and they can be computed as:

$$\nu_{b,k} = \sigma_{b,k} (\eta_{b,k} + \xi_{b,k})' = 1.$$

The test pairs defined by  $\nu_{b,k}$  may result in an error only if the transition of one or more side inputs violate timing constraints, that is are able to discover only multiple faults.

#### 4.3 Accounting for Hazards

#### 4.3.1 Hazards on side inputs

In order to keep the description of the method as simple as possible, in the previous analysis it was not accounted for possible hazards on the side inputs of b.

Before to describe how the method accounts for hazards, a brief remark of the kind of hazards existing is required. A module output may present two kinds of *static hazards* [21]: function and logic. *Function hazards* depend on the timing of block's inputs and the block's logic function, while *logic hazards* are implementation dependent. Since the presented method is independent of the implementation of logic blocks, only function hazards will be considered.

The signal model described in section 4.1 can be modified in order to describe the possible presence of hazards that are characterized by the boolean variables  $h_i$  and  $\chi_i$ . The first variable denotes the possible presence of a hazard (of course, all primary inputs have  $h_i = 0$ ), while the second one describes the uncertainty on the value that is sampled in case the hazard is active when the sampling instant occurs. This latter event occurs only if a timing violation is in order, because, at the sampling instant, the signal has not yet stabilized to its final value. Therefore, the value of a signal  $s_i$  can be written as:

$$w_i = (\alpha_i' v_i + \alpha_i (h_i' u_i + h_i \chi_i)) \tag{4.14}$$

For the considered logic block, let  $H_b = (h_0, h_1, \ldots, h_{n-1})$  and  $\chi_b = (\chi_0, \chi_1, \ldots, \chi_{n-1})$ , be the ordered sets of such variables. Robust test conditions can be expressed by imposing that, for all inputs but the on-path one, fault detection is independent of the value of  $\alpha_j$  and, for all inputs, fault detection is independent of  $\chi_j$ .

Therefore, equation 4.6 can be rewritten as:

$$\rho_{b,k} = \left(\sum_{\substack{j \neq k \ j=0}}^{n-1} \frac{\partial \sigma}{\partial \alpha_j} + \sum_{j=0}^{n-1} \frac{\partial \sigma}{\partial \chi_j} + \sum_{\substack{i \neq k \ j=k \ i=0}}^{n-2} \sum_{\substack{j=i+1 \ j=i+1}}^{n-1} \frac{\partial^2 \sigma}{\partial \alpha_i \partial \alpha_j} + \sum_{\substack{i \neq k \ i=0}}^{n-1} \sum_{\substack{j=0 \ j=i+1}}^{n-1} \frac{\partial^2 \sigma}{\partial \chi_i \partial \chi_j} + \sum_{i=0}^{n-2} \sum_{\substack{j=i+1 \ j=i+1}}^{n-1} \frac{\partial^2 \sigma}{\partial \chi_i \partial \chi_j} + \dots \right)'$$

$$\cdots + \frac{\partial^{2n-1} \sigma}{\partial \alpha_0 - \partial \alpha_{k-1} \partial_{k+1} - \partial \alpha_{n-1} \partial \chi_0 \partial \chi_1 - \partial \chi_{n-1}}$$

(4.15)

that, in a more compact way, is:

$$\rho_{b,k} = \mathcal{D}(\sigma, \alpha_{b,k} \cup \chi_b)'.$$

Since the different effects of hazards are not of interest for the method, a relevant simplification can be made by considering  $\chi_i = X \, \forall i$ , where X is a boolean variable representing an unknown value. In this way, equation 4.15 becomes:

$$\rho_{b,k} = \left(\sum_{\substack{j \neq k \ j=0}}^{n-1} \frac{\partial \sigma}{\partial \alpha_j} + \frac{\partial \sigma}{\partial X} + \sum_{\substack{i \neq k \ i=0}}^{n-2} \sum_{\substack{j \neq k \ j=i+1}}^{n-1} \frac{\partial^2 \sigma}{\partial \alpha_i \partial \alpha_j} + \sum_{\substack{i \neq k \ i=0}}^{n-1} \frac{\partial^2 \sigma}{\partial \alpha_i \partial X} + \dots \right)$$

$$\cdots + \frac{\partial^n \sigma}{\partial \alpha_0 - \partial \alpha_{k-1} \partial \alpha_{k+1} - \partial \alpha_{n-1} \partial X}$$

(4.16)

or, in a more compact formulation:

$$\rho_{b,k} = \mathcal{D}(\sigma, \alpha_k \cup X)'$$

.

Equation 4.6 can be used to calculate  $\eta_{b,k}$  and also in this case an iterative or recursive computation can be used. Considering a simple example  $(f_b = v_0 v_1)$ , where  $s_0$  is supposed to be the on-path input, it is obtained:

$$\eta_{b,c} = u_0' u_1 v_1 h_0' + u_0 u_1' h_0' h_1' v_0 v_1$$

. The first product corresponds to the case of a rising transition. In order to satisfy it, the on-path transition (i.e. that on  $s_0$ ) must be hazard free and the side input must simply be at high logic value with the second test vector. Note that the constraints on the on-path input signal are automatically satisfied by considering the logic feeding such a signal. The second product

term, instead, corresponds to a falling transition. In this case, both the inputs should be hazard free, while the side input should remain stable at the high logic value. Again, these conditions correspond to the usual constraints used in the robust testing of an AND gate.

#### 4.3.2 Evaluation of hazards within the circuit

As shown in the previous section, the robust test conditions may include constraints on the variables  $(h_i)$  denoting the possible presence of hazards on path's side inputs. Test generation should provide hazard-free transitions when required by equation 4.16, therefore, the circuit should be characterized from the point of view of hazards.

Within the *timing arcs delay model*, a hazard may be present at the output of a functional block because of:

- a) the generation of a hazard caused by hazard-free transitions at the block's inputs;

- b) the propagation of an input hazard.

Note again that (logic) hazards generated because of the internal timing of the considered block are neglected.

In the actual circuit, the hazards generated in case a) depend on the input vectors applied to the considered module c, the timing of the input signals of c and the delays that are related to such input signals. Since an unbounded delay model is used, the characterization of all the possible hazards occurring at the output of c is required.

To this purpose, the signal representation introduced in section 4.3 will be used, but in this case  $w_i$  does not represent the sampled value of  $s_i$ ; it simply represents any value after  $u_i$  and before  $v_i$ .

Under such hypothesis,  $\gamma_c$  describes the possible presence of a static hazard at the output of c:

$$\gamma_c = (u_c \oplus w_c)(w_c \oplus v_c) = 1 \tag{4.17}$$

where,  $u_c$ ,  $w_c$  and  $v_c$  can be computed as a function of the values charac-

terizing the n inputs of c:

$$u_c = f_c(u_0, u_1, \dots, u_{n-1}),$$

$w_c = f_c(w_0, w_1, \dots, w_{n-1}),$

$v_c = f_c(v_0, v_1, \dots, v_{n-1}).$

Note that the condition in equation 4.17 can be satisfied only if  $u_c = v_c$ .

It must be noted that, in this approach, dynamic hazards are not considered, because they would be relevant only if constraints on side inputs specify both  $u_i$  and  $v_i$  with  $u_i \neq v_i$ . This, however, contradicts robustness hypothesis because in such a case the value sampled at the output of the considered block would depend on the side input's timing. In any case, the proposed method can be easily extended to handle dynamic hazards.

In order to compute  $w_c$ , a block's input signal  $s_i$  is characterized by  $u_i$ ,  $v_i$  and by:

$$w_i = (\alpha_i' v_i + \alpha_i (h_i' u_i + h_i X)),$$

thus accounting for both the generation of a function hazard at the output of c and the propagation of input hazards described by the variables  $h_i \in H_c$ .

In equation 4.17,  $\gamma'_c$  describes the possible conditions that, depending also on the macro's inputs timing as defined by the values of the variables in  $\alpha_c$ , cannot give rise to the possible presence of hazards. In the context of robust testing, the input values that ensure a hazard-free output independently of their relative timing are required. Therefore, the difference operator ( $\mathcal{D}$ ) is used again to provide the configurations of  $U_c$ ,  $V_c$  and  $H_c$ which, independently of the actual ICs timing (a part from the timing internal to c), cannot give rise to the generation of a hazard. The characteristic function  $(n_c(U_c, V_c, \alpha, X))$  of this set of configurations can be computed as:

$$n_c(U_c, V_c, \alpha, X) = \gamma_c' \mathcal{D}(\gamma_c', \alpha \cup \{X\})'. \tag{4.18}$$

Consistently with its definition, the function  $h_c = n'_c$  describes the input configuration that may produce an output hazard.

As an example, considering the function  $f_c = v_0 v_1 + v_2$  again, it is:

$$\begin{split} n_{out} = & v_0 v_1 u_0 u_1 h_0' h_1' + v_0 v_1 u_0 u_2' h_0' h_1' h_2' + v_0' v_2' u_0' h_0' h_2' + \\ + & v_0' u_0' u_2' h_0' h_2' + v_1 u_0' u_2' h_0' h_1' h_2' + v_1' v_2' u_1' h_1' h_2' + v_1' u_1' u_2' h_1' h_2' + \\ + & v_2 u_2 h_2' + v_2' u_0 u_1 h_0' h_1' h_2' + u_0 u_1 u_2 h_0' h_1' h_2' + u_0' u_1' u_2' h_0' h_1' h_2', \end{split}$$

that denotes all the possible hazard-free conditions.