DOTTORATO DI RICERCA IN "INGEGNERIA ELETTRONICA"

CICLO XXI

COORDINATORE Prof. Bertozzi Davide

## Driving the Network-on-Chip Revolution to Remove the Interconnect Bottleneck in Nanoscale Multi-Processor Systems-on-Chip.

Settore Scientifico Disciplinare ING-INF/01

**Dottorando** Dott. Medardoni Simone **Tutore** Prof. Bertozzi Davide

(firma)

(firma)

Anni 2006/2008

## ABSTRACT

The sustained demand for faster, more powerful chips has been met by the availability of chip manufacturing processes allowing for the integration of increasing numbers of computation units onto a single die. The resulting outcome, especially in the embedded domain, has often been called SYSTEM-ON-CHIP (SoC) or MULTI-PROCESSOR SYSTEM-ON-CHIP (MP-SoC).

MPSoC design brings to the foreground a large number of challenges, one of the most prominent of which is the design of the chip interconnection. With a number of on-chip blocks presently ranging in the tens, and quickly approaching the hundreds, the novel issue of how to best provide on-chip communication resources is clearly felt.

NETWORKS-ON-CHIPS (NoCs) are the most comprehensive and scalable answer to this design concern. By bringing large-scale networking concepts to the on-chip domain, they guarantee a structured answer to present and future communication requirements. The point-to-point connection and packet switching paradigms they involve are also of great help in minimizing wiring overhead and physical routing issues. However, as with any technology of recent inception, NoC design is still an evolving discipline. Several main areas of interest require deep investigation for NoCs to become viable solutions:

- The design of the NoC architecture needs to strike the best tradeoff among performance, features and the tight area and power constraints of the onchip domain.

- Simulation and verification infrastructure must be put in place to explore, validate and optimize the NoC performance.

- NoCs offer a huge design space, thanks to their extreme customizability in terms of topology and architectural parameters. Design tools are needed to prune this space and pick the best solutions.

- Even more so given their global, distributed nature, it is essential to evaluate the physical implementation of NoCs to evaluate their suitability for next-generation designs and their area and power costs.

This dissertation performs a design space exploration of network-on-chip architectures, in order to point-out the trade-offs associated with the design of each individual network building blocks and with the design of network topology overall. The design space exploration is preceded by a comparative analysis of state-of-the-art interconnect fabrics with themselves and with early networkon-chip prototypes. The ultimate objective is to point out the key advantages that NoC realizations provide with respect to state-of-the-art communication infrastructures and to point out the challenges that lie ahead in order to make this new interconnect technology come true. Among these latter, technologyrelated challenges are emerging that call for dedicated design techniques at all levels of the design hierarchy. In particular, leakage power dissipation, containment of process variations and of their effects. The achievement of the above objectives was enabled by means of a NoC simulation environment for cycleaccurate modelling and simulation and by means of a back-end facility for the study of NoC physical implementation effects. Overall, all the results provided by this work have been validated on actual silicon layout.

ii

# Contents

| 1        | Intr                                            | roduction                                                | <b>1</b>  |  |  |  |  |

|----------|-------------------------------------------------|----------------------------------------------------------|-----------|--|--|--|--|

| <b>2</b> | State of the Art SoC Communication Architecture |                                                          |           |  |  |  |  |

|          | 2.1                                             | Introduction                                             | 5         |  |  |  |  |

|          | 2.2                                             | AMBA Bus                                                 | 6         |  |  |  |  |

|          |                                                 | 2.2.1 AMBA System Bus                                    | 7         |  |  |  |  |

|          |                                                 | 2.2.2 AMBA AHB Basic Operation                           | 8         |  |  |  |  |

|          |                                                 | 2.2.3 Advanced Peripheral Bus (APB)                      | 8         |  |  |  |  |

|          |                                                 | 2.2.4 Advanced AMBA Evolutions                           | 9         |  |  |  |  |

|          | 2.3                                             | CoreConnect Bus                                          | 12        |  |  |  |  |

|          |                                                 | 2.3.1 Processor Local Bus (PLB)                          | 13        |  |  |  |  |

|          |                                                 | 2.3.2 On-Chip Peripheral Bus (OPB)                       | 14        |  |  |  |  |

|          |                                                 | 2.3.3 Device Control Register Bus (DCR)                  | 15        |  |  |  |  |

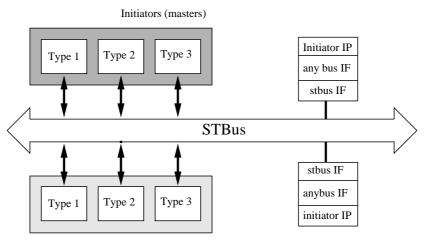

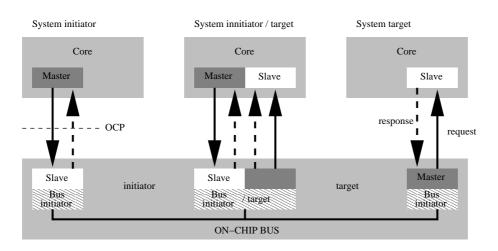

|          | 2.4                                             | STBus                                                    | 15        |  |  |  |  |

|          |                                                 | 2.4.1 Bus topologies                                     | 17        |  |  |  |  |

|          | 2.5                                             | WishBone                                                 | 17        |  |  |  |  |

|          |                                                 | 2.5.1 The Wishbone Bus Transactions                      | 18        |  |  |  |  |

|          | 2.6                                             | SiliconBackplane MicroNetwork                            | 18        |  |  |  |  |

|          |                                                 | 2.6.1 System Interconnect Bandwidth                      | 20        |  |  |  |  |

|          |                                                 | 2.6.2 Configuration Resources                            | 20        |  |  |  |  |

|          | 2.7                                             | Other On-Chip Interconnects                              | 20        |  |  |  |  |

|          |                                                 | 2.7.1 Peripheral Interconnect Bus (PI-Bus)               | 20        |  |  |  |  |

|          |                                                 | 2.7.2 AVALON                                             | 21        |  |  |  |  |

|          |                                                 | 2.7.3 CoreFrame                                          | 22        |  |  |  |  |

|          | 2.8                                             | Conclusions                                              | 23        |  |  |  |  |

| 3        | Ans                                             | alysing the communication in a memory-centric industrial |           |  |  |  |  |

| 0        |                                                 |                                                          | <b>27</b> |  |  |  |  |

|          | 3.1                                             | Introduction                                             | 27        |  |  |  |  |

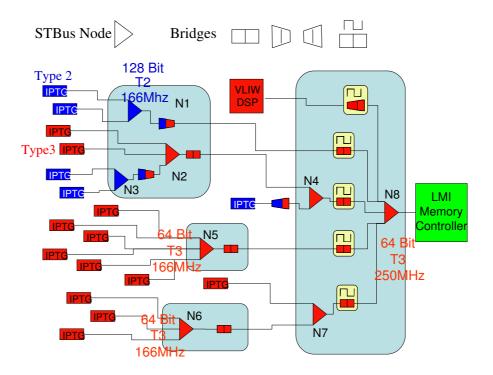

|          | 3.2                                             | MPSIM, a SystemC Platform Simulation                     | 28        |  |  |  |  |

|          | 3.3                                             | MPSoC platform modelling                                 | 30        |  |  |  |  |

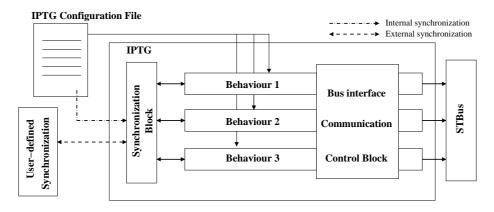

|          |                                                 | 3.3.1 STBus platform component models                    | 32        |  |  |  |  |

|          |                                                 | 3.3.2 Architectural variants                             | 34        |  |  |  |  |

|          | 3.4                                             | Interaction between communication and memory sub-systems | 36        |  |  |  |  |

|          |                                                 | 3.4.1 Single-layer architecture                          | 36        |  |  |  |  |

|          |                                                 | 3.4.2 Multi-layer architecture                           | 37        |  |  |  |  |

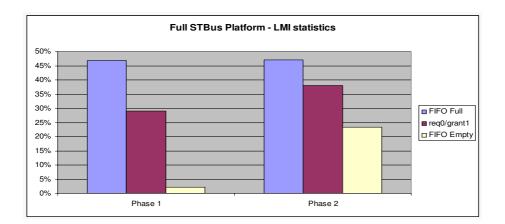

|          | 3.5                                             | Fine-grain platform performance analysis                 | 40        |  |  |  |  |

|          | 3.6                                             | Summary                                                  | 41        |  |  |  |  |

|          |                                                 |                                                          |           |  |  |  |  |

|          | 3.7               | Conclusion                                                     | 42              |

|----------|-------------------|----------------------------------------------------------------|-----------------|

| <b>4</b> | Net               | work-on-Chip: An Interconnect Fabric For MPSoCs                | 49              |

|          | 4.1               | Introduction                                                   | 49              |

|          | 4.2               | Design Challenges For On-Chip Communication Architectures      |                 |

|          |                   | 4.2.1 Technology challenges                                    |                 |

|          |                   | 4.2.2 Scalability challenges                                   |                 |

|          |                   | 4.2.3 Design productivity challenges                           |                 |

|          | 4.3               | Network-On-Chip Architecture                                   |                 |

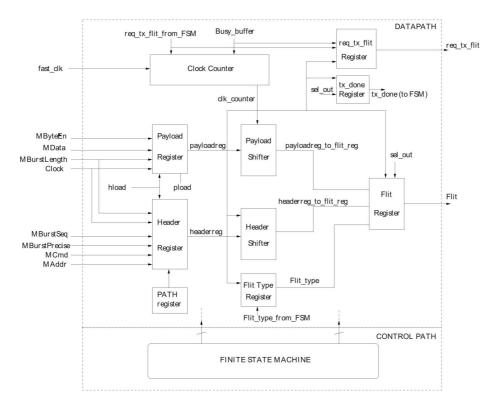

|          | 4.4               | Network Interface                                              | 56              |

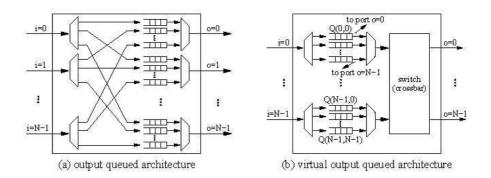

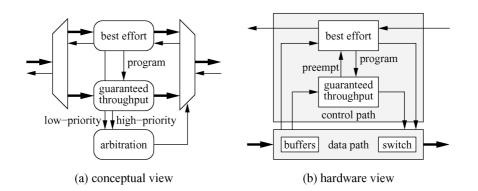

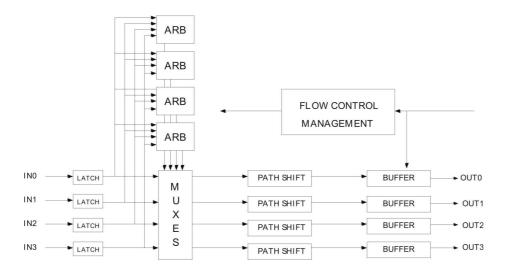

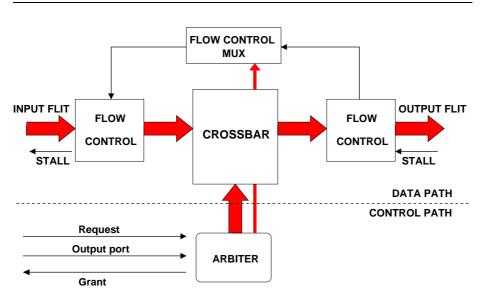

|          | 4.5               | Switch Architecture                                            | 60              |

|          |                   | 4.5.1 Æthereal                                                 | 62              |

|          |                   | 4.5.2 Xpipes Lite                                              |                 |

|          | 4.6               | Link Design                                                    |                 |

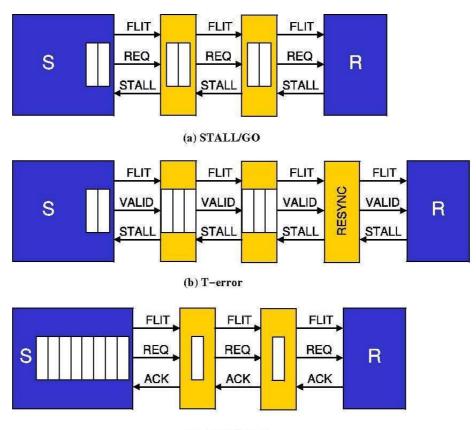

|          |                   | 4.6.1 Stall/Go                                                 |                 |

|          |                   | 4.6.2 T-Error                                                  |                 |

|          |                   | 4.6.3 Ack/Nack                                                 |                 |

|          | 4.7               | NoC design challenges                                          |                 |

|          | 4.8               | Conclusion                                                     |                 |

|          | 4.0               |                                                                |                 |

| 5        | <b>Swi</b><br>5.1 | tches: Architecture, Analysys and Optimization<br>Introduction | <b>73</b><br>73 |

|          |                   |                                                                |                 |

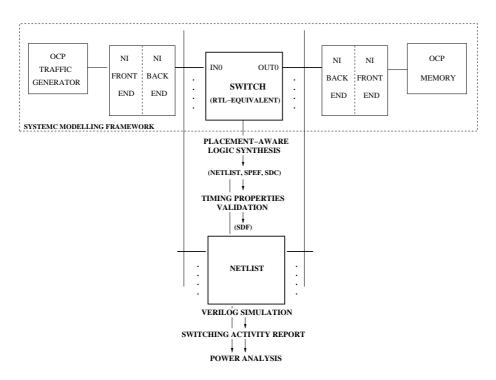

|          | 5.2               | Modelling and synthesis flow                                   |                 |

|          | 5.3               | Basic switching fabric                                         |                 |

|          | 5.4               | Control and datapath decoupling                                |                 |

|          | 5.5               | Spanning the area-latency-power trade-off                      |                 |

|          |                   | 5.5.1 Selection of switch architectures                        |                 |

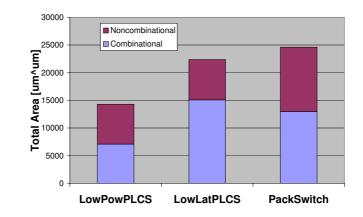

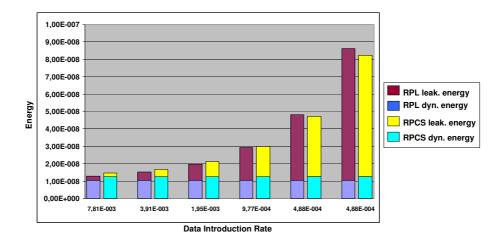

|          |                   | 5.5.2 Area comparative analysis                                |                 |

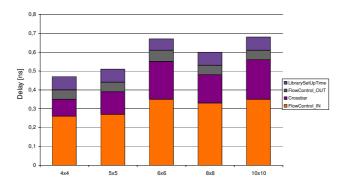

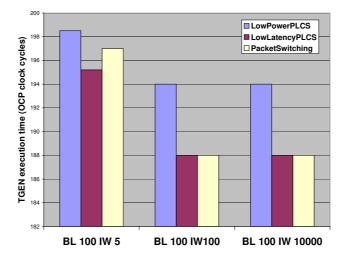

|          |                   | 5.5.3 Performance comparative analysis                         |                 |

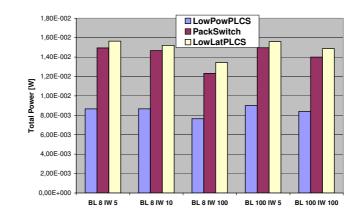

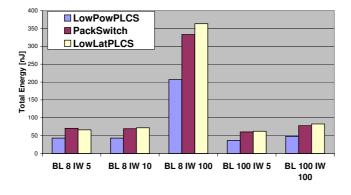

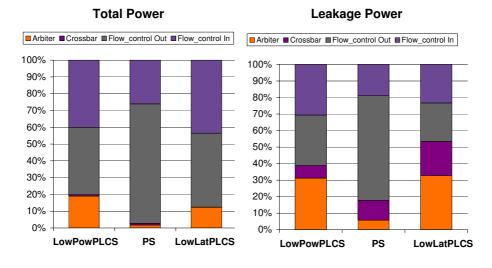

|          |                   | 5.5.4 Power/energy comparative analysis                        |                 |

|          | 5.6               | Conclusions                                                    | 84              |

| 6        | Net               | work Interface: Architecture, Analysys and Optimization        | 87              |

|          | 6.1               | Design requirements                                            | 88              |

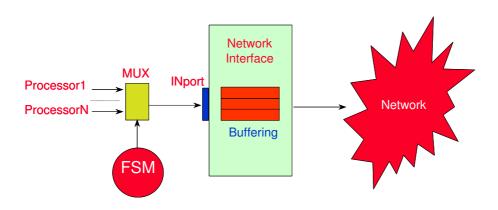

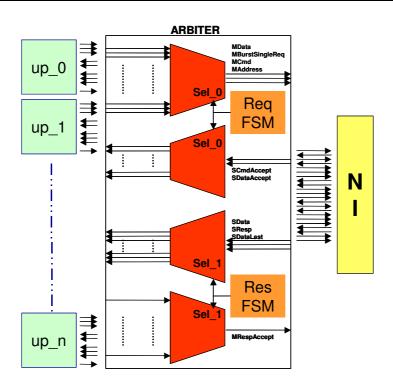

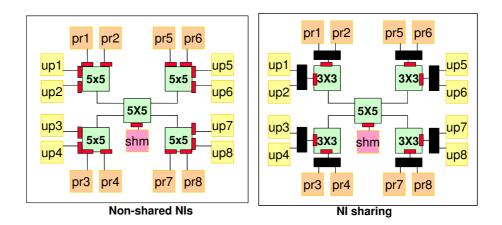

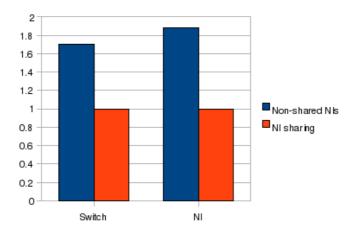

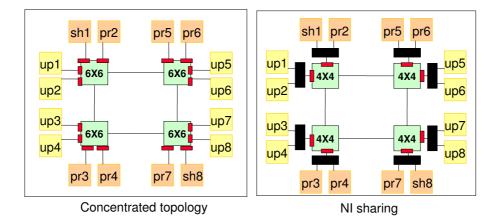

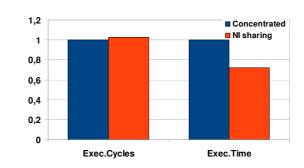

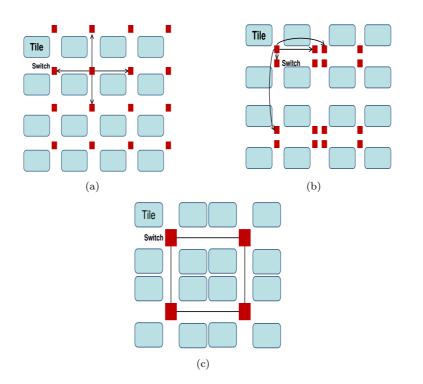

|          | 6.2               | NI sharing architectures                                       | 90              |

|          |                   | 6.2.1 Network interface architecture                           | 90              |

|          |                   | 6.2.2 Merger architecture                                      |                 |

|          | 6.3               | Optimizations                                                  |                 |

|          | 6.4               | Synthesis results                                              | 93              |

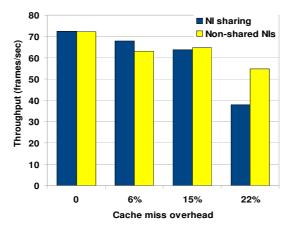

|          | 6.5               | Basic performance tests                                        | 94              |

|          | 6.6               | System-level analysis                                          | 96              |

|          | 0.0               | 6.6.1 Application-specific topology                            | 96              |

|          |                   | 6.6.2 General purpose topology                                 | 98              |

|          | 6.7               | Conclusions                                                    |                 |

|          | 0.7               |                                                                | 100             |

| 7        |                   | igning Regular Network-on-Chip Topologies under Technol        |                 |

|          |                   | and Architecture Constraints                                   | 105             |

|          | 7.1               | Backend synthesis flow                                         |                 |

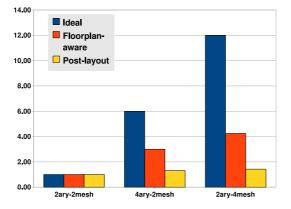

|          | 7.2               | Topology exploration                                           |                 |

|          |                   | 7.2.1 NoC architecture                                         | 108             |

|   |                                                                              | 7.2.2 Topologies under test: $k$ -ary $n$ -meshes $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                       | 9                                      |

|---|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   |                                                                              | 7.2.3 Topologies under test: $k$ -ary $n$ -Tree $\ldots \ldots $                                                                                                                                                                                                                                                                                                                                                               | 1                                      |

|   | 7.3                                                                          | Physical design: k-ary n-meshes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                      |

|   |                                                                              | 7.3.1 16 tile networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                                      |

|   |                                                                              | 7.3.2 64 tile networks $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $11$                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

|   | 7.4                                                                          | Physical design: k-ary n-Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

|   | 7.5                                                                          | Post-Layout analysis: $k$ -ary $n$ -mesh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |

|   |                                                                              | 7.5.1 $16$ tile $\ldots$ $\ldots$ $11$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

|   |                                                                              | 7.5.2 64 tile $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

|   | 7.6                                                                          | Post-Layout analysis: $k$ -ary $n$ -Tree $\ldots \ldots $                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|   | 7.7                                                                          | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

|   |                                                                              | 7.7.1 $k$ -ary $n$ -meshes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |

|   |                                                                              | 7.7.2 $k$ -ary $n$ -Tree $\ldots$ 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |

|   |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                      |

| 8 | Eme                                                                          | rging Issue 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                      |

|   | 8.1                                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                      |

|   | 8.2                                                                          | Architectural Implications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                      |

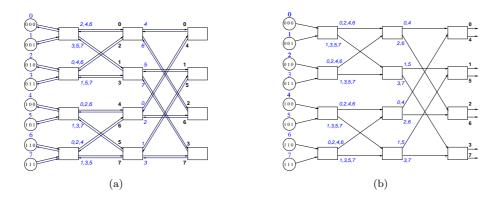

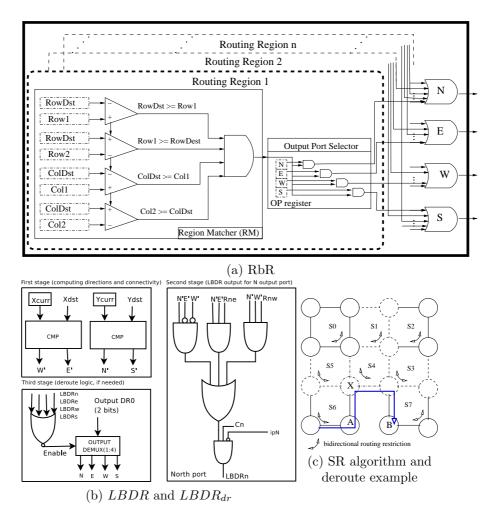

|   |                                                                              | 8.2.1 Routing Mechanisms and Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                                      |

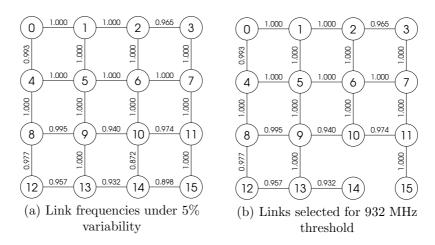

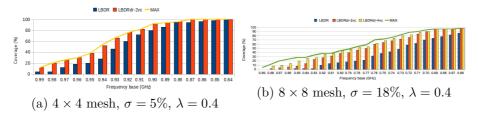

|   |                                                                              | 8.2.2 Modelling within-die variability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                      |

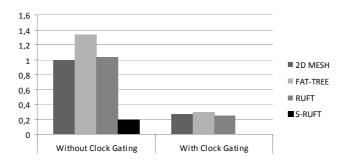

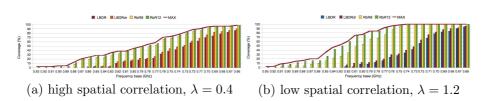

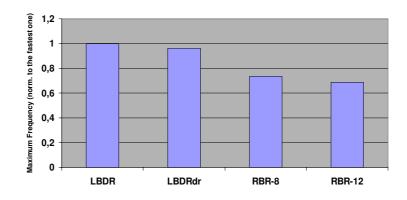

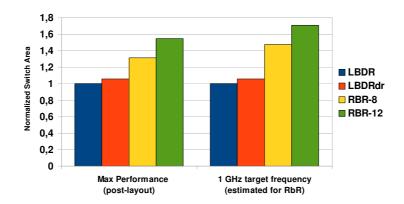

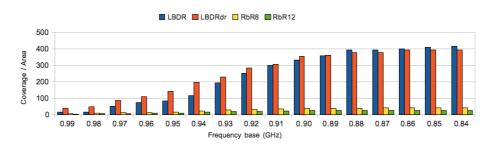

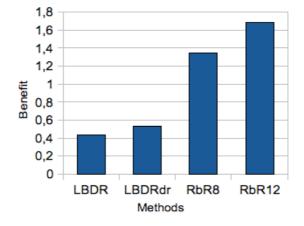

|   |                                                                              | 8.2.3 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                      |

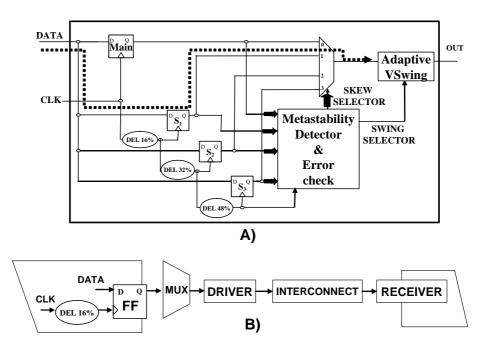

|   | 8.3                                                                          | Circuit Implications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                                      |

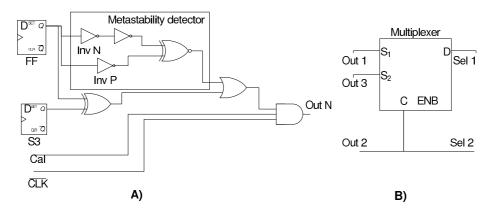

|   |                                                                              | 8.3.1 Self-correcting flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                      |

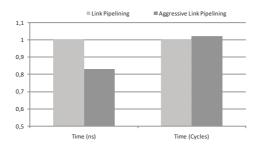

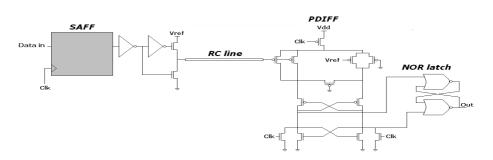

|   |                                                                              | 8.3.2 Link Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                      |

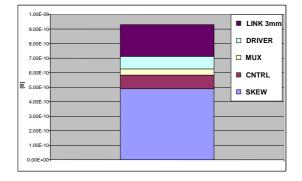

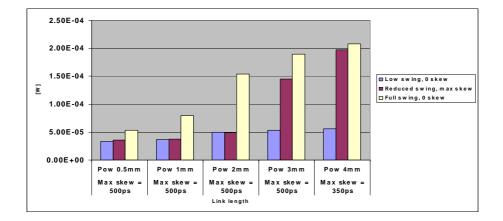

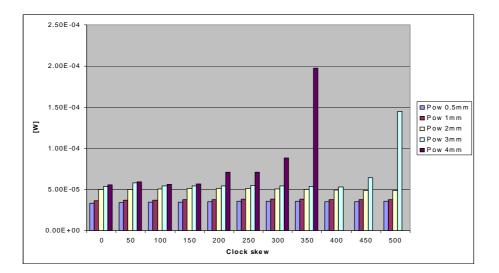

|   |                                                                              | 8.3.3 Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                      |

|   |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                      |

|   | 8.4                                                                          | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                                      |

|   | -                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                      |

| 9 | Pow                                                                          | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| 9 | Pow<br>Sens                                                                  | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive Technologies 163                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                      |

| 9 | Pow<br>Sens<br>9.1                                                           | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive Technologies 163<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>3</b><br>3                          |

| 9 | Pow<br>Sens                                                                  | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive Technologies 16<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>3</b><br>3<br>5                     |

| 9 | Pow<br>Sens<br>9.1                                                           | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive Technologies 16<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>3</b><br>3<br>5<br>5                |

| 9 | Pow<br>Sens<br>9.1                                                           | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive Technologies 163<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>3</b><br>3<br>5<br>5<br>5           |

| 9 | Pow<br>Sens<br>9.1<br>9.2                                                    | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive Technologies 163<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>3</b><br>3<br>5<br>5<br>5<br>7      |

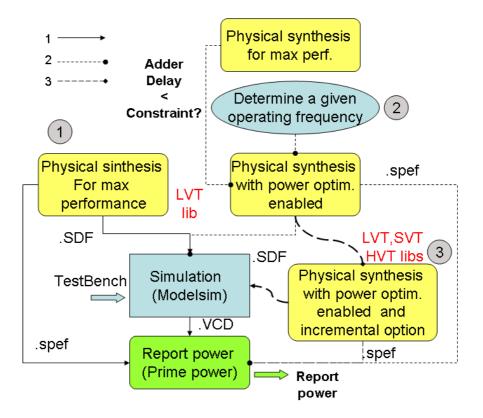

| 9 | Pow<br>Sens<br>9.1                                                           | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive Technologies163Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow16Experimental results16                                                                                                                                                                                                                                                                                   | $3 \\ 3 \\ 5 \\ 5 \\ 7 \\ 7$           |

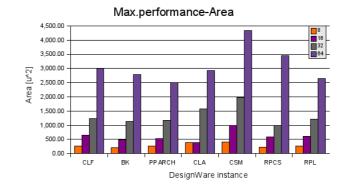

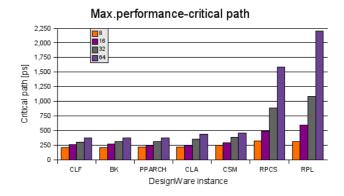

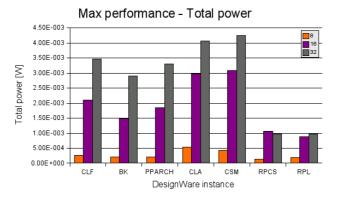

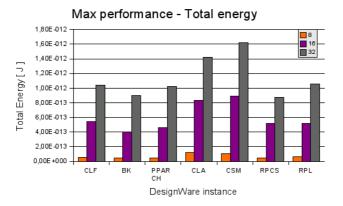

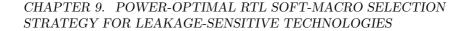

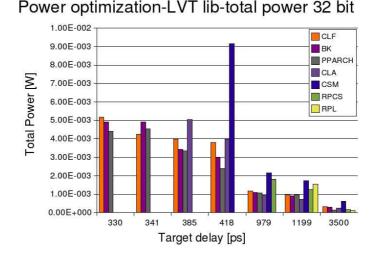

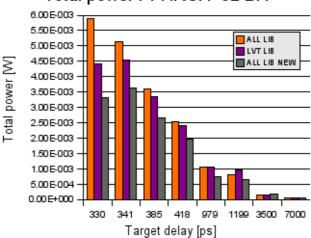

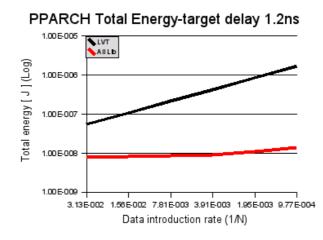

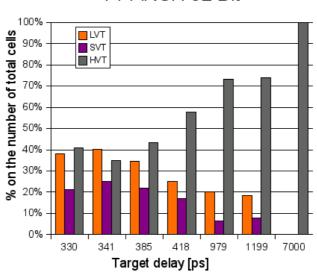

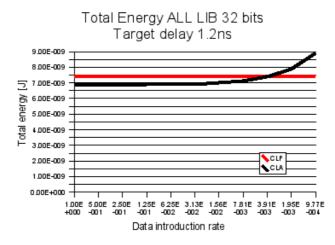

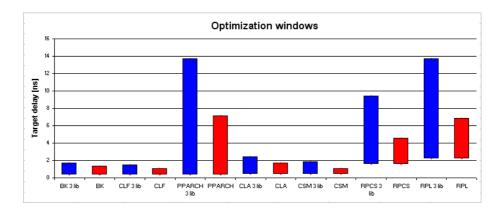

| 9 | Pow<br>Sens<br>9.1<br>9.2                                                    | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive Technologies163Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow16Synthesis flow169.2.3Later optimized synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units16                                                                                                                                                                        | $3 \\ 3 \\ 5 \\ 5 \\ 7 \\ 7 \\ 7 \\ 7$ |

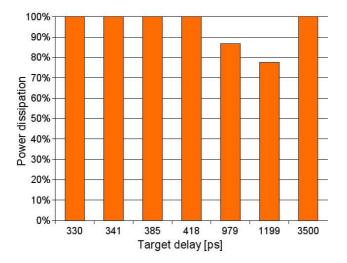

| 9 | Pow<br>Sens<br>9.1<br>9.2                                                    | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations17                                                                                                                                                                          | 3 3 5 5 5 7 7 1                        |

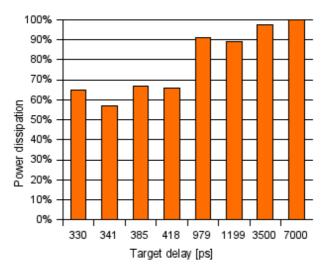

| 9 | Pow<br>Sens<br>9.1<br>9.2<br>9.3                                             | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17                                                                                                                                     | 3355577712                             |

| 9 | Pow<br>Sens<br>9.1<br>9.2<br>9.3                                             | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17                                                                                                                                   | 33555777125                            |

| 9 | Pow<br>Sens<br>9.1<br>9.2<br>9.3                                             | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17                                                                                                                                     | 33555777125                            |

|   | Pow<br>Sens<br>9.1<br>9.2<br>9.3<br>9.3                                      | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-itive Technologies16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17Conclusions17                                                                                         | 335557771256                           |

|   | Pow<br>Sens<br>9.1<br>9.2<br>9.3<br>9.3<br>9.4<br>9.5<br>Con                 | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17Conclusions17Elusion and Future work18                                                | <b>3</b> 35557771256<br><b>3</b>       |

|   | Pow<br>Sens<br>9.1<br>9.2<br>9.3<br>9.3<br>9.4<br>9.5<br><b>Con</b><br>10.1  | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17Conclusions17Conclusions18                                                            | <b>3</b> 35557771256<br><b>3</b> 3     |

|   | Pow<br>Sens<br>9.1<br>9.2<br>9.3<br>9.3<br>9.4<br>9.5<br>Com<br>10.1<br>10.2 | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17clusion and Future work18Future Work18                                                | <b>3</b> 35557771256<br><b>3</b> 34    |

|   | Pow<br>Sens<br>9.1<br>9.2<br>9.3<br>9.3<br>9.4<br>9.5<br>Com<br>10.1<br>10.2 | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17Conclusions18Future Work18Scientific Publication18                                    | <b>3</b> 35557771256<br><b>3</b> 344   |

|   | Pow<br>Sens<br>9.1<br>9.2<br>9.3<br>9.3<br>9.4<br>9.5<br>Com<br>10.1<br>10.2 | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17Conclusions18Future Work18Scientific Publication1810.3.1Proceedings18                 | <b>3</b> 35557771256 <b>3</b> 3445     |

|   | Pow<br>Sens<br>9.1<br>9.2<br>9.3<br>9.3<br>9.4<br>9.5<br>Com<br>10.1<br>10.2 | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17Conclusions18Future Work18Scientific Publication1810.3.1Proceedings1810.3.2Magazine18 | <b>3</b> 35557771256 <b>3</b> 34458    |

|   | Pow<br>Sens<br>9.1<br>9.2<br>9.3<br>9.3<br>9.4<br>9.5<br>Com<br>10.1<br>10.2 | er-Optimal RTL Soft-Macro Selection Strategy for Leakage-<br>itive TechnologiesIntroduction16Introduction16Synthesis methodology169.2.1Performance-optimized synthesis flow169.2.2Power-optimized synthesis flow169.2.3Multi-Vth synthesis flow169.2.3Multi-Vth synthesis flow169.3.1Energy characterization of adder units169.3.2The impact of power optimizations179.3.3The impact of multi-Vth design17Comparison with default DW selection strategy17Conclusions18Future Work18Scientific Publication1810.3.1Proceedings18                 | 3 3 5 5 5 7 7 7 1 2 5 6 3 3 4 4 5 8 9  |

## Chapter 1

## Introduction

Silicon vendors are constantly facing pressure to deliver feature-rich, highperformance, low-power, low-cost chips, in as short a time as possible. Luckily, silicon manufacturing techniques have been continuously perfected, following the well-known Moore's Law; this has provided the potential for answering customer demands.

However, along the years, an increasing gap has been observed among the number of available on-chip transistors and the capability of designers to make good use of them. As a consequence, some trends in chip design have become crystal clear:

- An increasing emphasis on modularity, reuse and parallelism is mandatory. Redesign from scratch is too time-consuming. Also, deploying multiple instances of existing computation blocks can be more efficient than developing more powerful blocks. Therefore, libraries of so-called INTELLEC-TUAL PROPERTY (IP) cores are increasingly becoming the foundation of platform development.

- Also based on the previous item, complexity is nowadays shifting from the development of functional units to the task of system integration. This is exacerbated by the fact that full designs are nowadays almost impossible to characterize in all possible operating conditions, leading to closure, optimization and verification issues.

- Software tools devoted to design automation are key at all levels. This applies to performance characterization, platform assembly and validation, physical implementation, etc.. Without efficient tools, the sheer complexity of billion-transistor designs and deep-submicron lithographic processes is impossible to tackle by designer teams of any size.

A typical outcome of these trends are today's MULTI-PROCESSOR-SYSTEMS-ON-CHIPS (MPSoCs). These are full-featured chips, composed of a variety of functional blocks, to the point of integrating the foundation of a whole system or device into a single die. MPSoCs are used in a variety of environments, including multimedia gadgets, gaming stations, smartphones, automotive equipment, healthcare devices, industrial machinery, aerospace control units, and many more. MPSoCs are built upon assemblies of IP cores, and rely extensively on COMPUTER AIDED DESIGN (CAD) tooling for initial design space exploration, system optimization, system verification, and physical implementation.

An increasingly critical piece of the MPSoC puzzle is the on-chip interconnection infrastructure. Today, even MPSoCs used in mid-range mobile phones can easily contain tens of IP cores, and new chips with more than a hundred such internal units are appearing for various applications. The trend expressing the number of IP cores that can be integrated on a chip is exponential, roughly doubling every 18 months. How to effectively provide communication resources among such a number of building blocks is clearly a challenge. In fact, it is likely a key factor in determining the success or failure of upcoming MPSoCs will be the ability to efficiently provide the communication backbone into which to seamlessly plug a variety of IP cores.

A comprehensive solution to on-chip interconnection issues has been proposed in the form of NETWORKS-ON-CHIPS (NoCs).

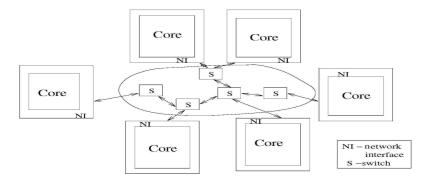

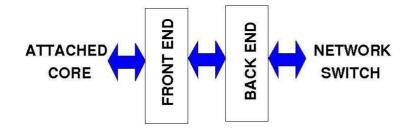

NoCs are packet-switching networks, brought to the on-chip level. The rationale is that, since the complexity of on-chip communication is rapidly approaching that of large area systems in terms of actors, it makes sense to reuse some of the solutions devised in the latter space. Therefore, NoCs are based upon topologies of switches (also called routers) distributing packets around, over point-to-point links. Since existing IP cores do not normally communicate by means of packets, NETWORK INTERFACES (NIS ) (also called network adapters) are in charge of protocol conversion; they convert commands appearing on the pinout of IP cores into packets, and vice versa at the receiving end of a transaction. NoCs have the potential to bring a large number of advantages to on-chip communication, such as:

- Virtually unlimited architectural scalability. As known from wide area networks, it is easy to comply with higher bandwidth requirements by larger numbers of cores simply by deploying more switches and links.

- Much better electrical performance. All connections are point-to-point. The length of inter-switch links is a design parameter that can be adjusted. The wire parallelism in links can be controlled at will, since packet transmission can be serialized. All these factors imply faster propagation times and total control over crosstalk issues.

- Also due to the possibility of having narrower links than in buses (e.g. 32 bits instead of 100), routing concerns are greatly alleviated, and wiring overhead is dramatically reduced. This leads to higher wire utilization and efficiency.

- Faster and easier design closure achievement. Physical design improvements make NoCs, in general, more predictable than buses. Therefore, it is more unlikely that costly respins will be required upon physical design and performance qualification.

- Better performance under load. Since the operating frequency can be higher than in buses, the data width is a parameter, and communication flows can be handled in parallel with suitable NoC topology design, virtually any bandwidth load can be tackled.

- More modular, plug&play-oriented approach to system assembly. IP cores are attached in point-to-point fashion to dedicated NIs; NIs can be specialized for any interface that may be needed, either industry standards such as AMBA AHB or any custom protocol. Potentially any core may be seamlessly attached to a NoC given the proper NI. Computation and communication concerns are clearly decoupled at the NI level.

- Potential for the development of streamlined design flows. While hierarchical buses are often assembled by hand and therefore must be tuned and validated with manual intervention, a network can be designed, optimized and verified by automated means, leading to large savings in design times, and getting a solution closer to optimality.

- A much larger design space. NoCs can be tuned in a variety of parameters (topology, buffering, data widths, arbitrations, routing choices, etc.), leading to higher chances of optimally matching design requirements. Being distibuted, modular structures, NoCs can also accommodate differently tuned regions. For example, some portions of a NoC could be tuned statically for lower resource usage and lower performance (e.g. by reducing the data width), or could dynamically adjust their mode of operation (e.g. frequency, voltage scaling).

At the same time, NoCs are facing a completely different set of constraints compared to wide area networks. While in the latter environment a switch is implemented with at least one dedicated chip, in a NoC the switch must occupy a tiny fraction of the chip real estate. This means that some of the principles acquired in wide area networking have to be revisited. Some of the challenges lying ahead of NoCs include:

- The tradeoffs among network features, area and power budgets have to be studied from scratch. Policies which are widely accepted in general networking (e.g. dynamic packet routing) must be reassessed to evaluate their impact on silicon area.

- Performance requirements are very different in the on-chip domain, also due to the completely different properties of on-chip wiring. Bandwidth milestones are much easier to achieve, since information transfer across on-chip wires is much faster than across long cables. Conversely, latency bounds are much stricter; while milliseconds or even hundreds of milliseconds are acceptable for wide area networks, IP cores on a chip normally require response times of few nanoseconds.

- Contrary to wide area networks, where nodes may often be dynamically connected to and disconnected from the network, in NoCs the set of attached IP cores is obviously fixed. In many applications, it is also relatively easy to statically characterize the traffic profiles of such IP cores. This opens up the possibility of thoroughly customizing NoCs for specific workloads. How to achieve this goal is, however, less clear.

- Design tools for NoCs can be developed, but, as above, how exactly is an open question. The customizability of NoCs, while an asset, is also an issue when it comes to devising tools capable of pruning the design space

in search of the optimal solutions. The problem is compounded by the need to take into account both architectural and physical properties; by the need to guarantee design closure; and by the need to validate that the outcome is fully functional, e.g. deadlock-free and compliant with performance objectives.

• NoCs are a recent technology, and as such, they are in need of the development of thorough infrastructure. In addition to design tools, this includes simulators, emulation platforms, and back-end flows for the implementation on APPLICATION-SPECIFIC INTEGRATED CIRCUITS (ASICS).

The main objective of this dissertation is to perform a design space exploration of network-on-chip architectures, in order to point-out the trade-offs associated with the design of each individual network building block and with the design of network topology overall. This exploration aims at providing guidelines to system designers as to the most suitable network design configuration to meet predefined performance, area and power constraints. The design space exploration is preceded by a comparative analysis of state-of-the-art interconnect fabrics with themselves and with early network-on-chip prototypes. The ultimate objective is to point out the key advantages that NoC realizations provide with respect to state-of-the-art communication infrastructures and to point out the challenges that lie ahead in order to make this new interconnect technology come true. Among these latter, technology-related challenges are emerging that call for dedicated design techniques at all levels of the design hierarchy. In particular, leakage power dissipation, containment of process variations and of their effects. The achievement of the above objectives was enabled by means of a NoC simulation environment for cycle-accurate modelling and simulation and by means of a back-end facility for the study of NoC physical implementation effects. Overall, all the results provided by this work have been validated on actual silicon layout.

## Chapter 2

# State of the Art SoC Communication Architecture

## 2.1 Introduction

The current high levels of on-chip integration allow for the implementation of increasingly complex Systems-on-Chip (SoCs), consisting of heterogeneous components such as general purpose processors, DSPs, coprocessors, memories, I/O units, and dedicated hardware accelerators.

In this context, Multi-Processor Systems-on-Chip (MPSoCs) are emerging as an effective solution to meet the demand for computational power posed by application domains such as network processors and parallel media processors. MPSoCs combine the advantages of parallel processing with the high integration levels of Systems-on-Chips (SoCs).

It is expected that future MPSoCs will integrate hundreds of processing units and storage elements, and their performance will be increasingly interconnectdominated [21]. Interconnect technology and architecture will become the limiting factor for achieving operational goals, and the efficient design of low-power, high-performance on-chip communication architectures will pose novel challenges. The main issue regards *scalability* of system interconnects, since the trend for system integration is expected to continue. State-of-the-art on-chip buses rely on shared communication resources and on an arbitration mechanism which is in charge of serializing bus access requests. This widely adopted solution unfortunately suffers from power and performance scalability limitations, therefore a lot of effort is being devoted to the development of advanced bus topologies (e.g., partial or full crossbars, bridged buses) and protocols, some of them already implemented in commercially available products. In the long run, a more aggressive approach will be needed, and a design paradigm shift will most probably lead to a packetized on-chip communication based on micronetworks of interconnects or Networks-on-Chip (NoCs) [17, 15].

This chapter focuses on state-of-the-art SoC communication architectures, providing an overview of the most relevant ones from an industrial and research

## CHAPTER 2. STATE OF THE ART SOC COMMUNICATION ARCHITECTURE

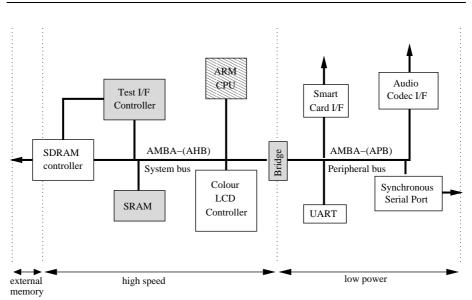

Figure 2.1: Schematic architecture of AMBA bus.

viewpoint. Open bus specifications such as AMBA and CoreConnect will be obviously described more in detail, providing the background which is needed to understand the necessarily more general description of proprietary industrial bus architectures, while at the same time being able to assess their contribution to the advance in the field.

## 2.2 AMBA Bus

AMBA (Advanced Micro-Controller Bus Architecture) is a bus standard which was originally conceived by ARM to support communication among ARM processor cores. However, nowadays AMBA is one of the leading on-chip busing systems because it is licensed and deployed for use with third party IP cores [1]. Designed for custom silicon, the AMBA specification provides standard bus protocols for connecting on-chip components, custom logic and specialized functions. These bus protocols are independent of the ARM processor and generalized for different SoC structures.

AMBA defines a segmented bus architecture, wherein two bus segments are connected with each other via a bridge that buffers data and operations between them. A system bus is defined, which provides a high-speed, high-bandwidth communication channel between embedded processors and high-performance peripherals. Two system buses are actually specified: the AMBA High-Speed Bus (AHB) and the Advanced System Bus (ASB).

Moreover, a low-performance and low power *peripheral bus* (called *Advanced Peripheral Bus, APB*) is specified, which accommodates communication with general purpose peripherals and is connected to the system bus via a bridge, acting as the only APB master. The overall AMBA architecture is illustrated in figure 2.1.

### 2.2.1 AMBA System Bus

ASB is the first generation of AMBA system bus, and sits above APB in that it implements the features required for high-performance systems including burst transfers, pipelined transfer operation and multiple bus masters. AHB is a later generation of AMBA bus which is intended to address the requirements of highperformance, high-clock synthesizable designs. ASB is used for simpler, more cost-effective designs whereas more sophisticated designs call for the employment of the AHB. For this reason, a detailed description of AHB follows.

The main features of AMBA AHB can be summarized as follows:

- *Multiple bus masters.* Optimized system performance is obtained by sharing resources among different bus masters. A simple request-grant mechanism is implemented between the arbiter and each bus master. In this way, the arbiter ensures that only one bus master is active on the bus and also that when no masters are requesting the bus a default master is granted.

- *Pipelined and burst transfers.* Address and data phases of a transfer occur during different clock periods. In fact, the address phase of any transfer occurs during the data phase of the previous transfer. This overlapping of address and data is fundamental to the pipelined nature of the bus and allows for high performance operation, while still providing adequate time for a slave to provide the response to a transfer. This also implies that ownership of the data bus is delayed with respect to ownership of the address bus. Moreover, support for burst transfers allows for efficient use of memory interfaces by providing transfer information in advance.

- *Split transactions.* They maximize the use of bus bandwidth by enabling high latency slaves to release the system bus during dead time while they complete processing of their access requests.

- Wide data bus configurations. Support for high-bandwidth data-intensive applications is provided using wide on-chip memories. System buses support 32, 64, and 128-bit data-bus implementations with a 32-bit address bus, as well as smaller byte and half-word designs.

- Non-tristate implementation. AMBA AHB implements a separate read and write data bus in order to avoid the use of tristate drivers. In particular, master and slave signals are multiplexed onto the shared communication resources (read and write data buses, address bus, control signals).

- A typical AMBA AHB system contains the following components:

- **AHB master:** Only one bus master at a time is allowed to initiate and complete read and write transactions. Bus masters drive out the address and control signals and the arbiter determines which master has its signals routed to all of the slaves. A central decoder controls the read data and response signal multiplexor, which selects the appropriate signals from the slave that has been addressed.

- **AHB slave:** It signals back to the active master the status of the pending transaction. It can indicate that the transfer completed successfully, or

that there was an error or that the master should retry the transfer or indicate the beginning of a split transaction.

- **AHB arbiter:** The bus arbiter serializes bus access requests. The arbitration algorithm is not specified by the standard and its selection is left as a design parameter (fixed priority, round-robin, latency-driven, etc.), although the request-grant based arbitration protocol has to be kept fixed.

- **AHB decoder:** This is used for address decoding and provides the select signal to the intended slave.

#### 2.2.2 AMBA AHB Basic Operation

In a normal bus transaction, the arbiter grants the bus to the master until the transfer completes and the bus can then be handed over to another master. However, in order to avoid excessive arbitration latencies, the arbiter can break up a burst. In that case, the master must re-arbitrate for the bus in order to complete the remaining data transfers.

A basic AHB transfer consists of four clock cycles. During the first one, the request signal is asserted, and in the best case at the end of the second cycle a grant signal from the arbiter can be sampled by the master. Then, address and control signals are asserted for slave sampling on the next rising edge, and during the last cycle the data phase is carried out (read data bus driven or information on the write data bus sampled). A slave may insert wait states into any transfer, thus extending the data phase, and a ready signal is available for this purpose.

Four, eight and sixteen-beat bursts are defined in the AMBA AHB protocol, as well as undefined-length bursts. During a burst transfer, the arbiter rearbitrates the bus when the penultimate address has been sampled, so that the asserted grant signal can be sampled by the relative master at the same point where the last address of the burst is sampled. This makes bus master handover at the end of a burst transfer very efficient.

For long transactions, the slave can decide to split the operation warning the arbiter that the master should not be granted access to the bus until the slave indicates it is ready to complete the transfer. This transfer *splitting* mechanism is supported by all advanced on-chip interconnects, since it prevents high latency slaves from keeping the bus busy without performing any actual transfer of data. On the contrary, split transfers can significantly improve bus efficiency, i.e. reduce the number of bus busy cycles used just for control (e.g. protocol handshake) and not for actual data transfers. Advanced arbitration features are required in order to support split transfers, as well as more complex master and slave interfaces.

### 2.2.3 Advanced Peripheral Bus (APB)

The AMBA APB is intended for general-purpose low-speed low-power peripheral devices. It enables the connection to the main system bus via a bridge. All bus devices are slaves, the bridge being the only peripheral bus master.

This is a static bus that provides a simple addressing, with latched addresses and control signals for easy interfacing. ARM recommends a dual Read and Write bus implementation, but APB can be implemented with a single tristated data bus.

The main features of this bus are the following:

- Unpipelined architecture.

- Low gate count.

- Low power operation.

- Reduced loading of the main system bus is obtained by isolating the peripherals behind the bridge.

- Peripheral bus signals are only active during low-bandwidth peripheral transfers.

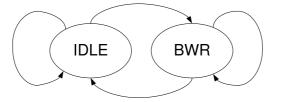

AMBA APB operation can be abstracted as a state machine with three states. The default state for the peripheral bus is *IDLE*, which switches to *SETUP* state when a transfer is required. SETUP state lasts just one cycle, during which the peripheral select signal is asserted. The bus then moves to *ENABLE* state, which also lasts only one cycle and which requires the address, control and data signals to remain stable. Then, if other transfers are to take place, the bus goes back to SETUP state, otherwise to IDLE. As can be observed, AMBA APB should be used to interface to any peripherals which are low-bandwidth and do not require the high performance of a pipelined bus interface.

### 2.2.4 Advanced AMBA Evolutions

Recently, some advanced specifications of AMBA bus have appeared, featuring increased performance and better link utilization. In particular, the *Multi-Layer AHB* and the *AMBA AXI* interconnect schemes will be briefly addressed in the following sub-sections.

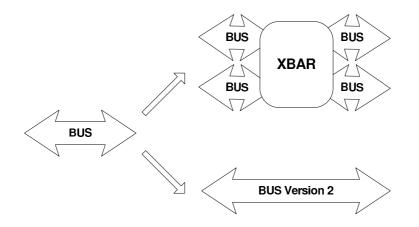

It should be observed that interconnect performance improvement can be achieved by adopting new topologies and by choosing new protocols, at the expense of silicon area. The former strategy leads from shared buses to bridged clusters, partial or full crossbars, and eventually to Networks-on-Chip (NoCs), in an attempt to increase available bandwidth and to reduce local contention. The latter strategy instead tries to maximize link utilization by adopting more sophisticated control schemes and thus permitting a better sharing of existing resources.

Multi-Layer AHB can be seen as an evolution of bus topology while keeping the AHB protocol unchanged. On the contrary, AMBA AXI represents an advanced interconnect fabric protocol.

#### Multi-layer AHB

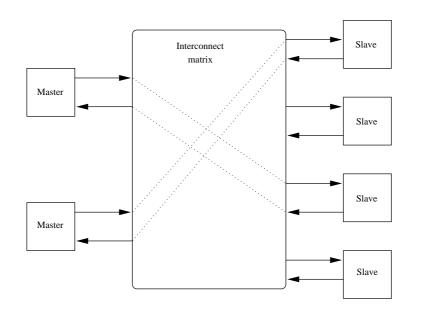

The Multi-Layer AHB specification emerges with the aim of increasing the overall bus bandwidth and providing a more flexible interconnect architecture with respect to AMBA AHB. This is achieved by using a more complex interconnection matrix which enables parallel access paths between multiple masters and slaves in a system [2].

CHAPTER 2. STATE OF THE ART SOC COMMUNICATION ARCHITECTURE

Figure 2.2: Schematic view of the multi-layer AHB interconnect

Therefore, the multi-layer bus architecture allows the interconnection of unmodified standard AHB master and slave modules with an increased available bus bandwidth. The resulting architecture becomes very simple and flexible: each AHB layer only has one master and no arbitration and master-to-slave muxing is needed. Moreover, the interconnect protocol implemented in these layers can be very simple: it does not have to support request and grant, nor retry or split transactions.

The additional hardware needed for this architecture with respect to the AHB is a multiplexor to connect the multiple masters to the peripherals and some point arbitration is also required when more than one master wants to access the same slave simultaneously.

Figure 2.2 shows a schematic view of the multi-layer concept. The interconnect matrix contains a decode stage for every layer in order to determine which slave is required during the transfer. The multiplexer is used to route the request from the specific layer to the desired slave.

The arbitration protocol decides the sequence of accesses of layers to slaves based on a priority assignment. The layer with lowest priority has to wait for the slave to be freed. Different arbitration schemes can be used, and every slave port has its own arbitration. Input layers can be served in a round-robin fashion, changing every transfer or every burst transaction, or based on a fixed priority scheme.

The number of input/output ports on the interconnect matrix is completely flexible and can be adapted to suit to system requirements. As the number of masters and slaves implemented in the system increases, the complexity of the interconnection matrix can become significant and some optimization techniques have to be used: defining multiple masters on a single layer, multiple slaves appearing as a single slave to the interconnect matrix, defining local slaves to a particular layer.

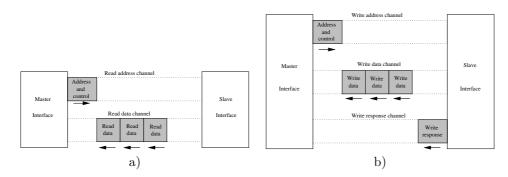

Figure 2.3: Architecture of transfers: a) Read operation; b) Write operation.

Finally, it is interesting to outline the capability of this topology to support multi-port slaves. Some devices, such as SDRAM controllers, work much more efficiently when processing transfers from different layers in parallel.

#### AMBA AXI Protocol

AXI is the latest generation AMBA interface. It is designed to be used as a high-speed submicron interconnect, and also includes optional extensions for low-power operation [3]. This high-performance protocol provides flexibility in the implementation of interconnect architectures while still keeping backward-compatibility with existing AHB and APB interfaces.

AMBA AXI builds upon the concept of point-to-point connection. AMBA AXI does not provide masters and slaves with visibility of the underlying interconnect, instead featuring the concept of *master interfaces* and symmetric *slave interfaces*. This approach, besides allowing seamless topology scaling, has the advantage of simplifying the handshake logic of attached devices, which only need to manage a point-to-point link.

To provide high scalability and parallelism, four different logical monodirectional channels are provided in AXI interfaces: an address channel, a read channel, a write channel and a write response channel. Activity on different channels is mostly asynchronous (*e.g.* data for a write can be pushed to the write channel before or after the write address is issued to the address channel), and can be parallelized, allowing multiple outstanding read and write requests.

Figure 2.3a shows how a read transaction uses the read address and read data channels. The write operation over the write address and write data channels is presented in Figure 2.3b.

As can be observed, the data is transferred from the master to the slave using a write data channel, and it is transferred from the slave to the master using a read data channel. In write transactions, in which all the data flows from the master to the slave, the AXI protocol has an additional write response channel to allow the slave to signal to the master the completion of the write transaction.

However, the AXI protocol is a master/slave-to-interconnect interface definition, and this enables a variety of different interconnect implementations. Therefore, the mapping of channels, as visible by the interfaces, to actual internal communication lanes is decided by the interconnect designer; single resources might be shared by all channels of a certain type in the system, or a variable amount of dedicated signals might be available, up to a full crossbar scheme. The rationale of this split-channel implementation is based upon the observation that usually the required bandwidth for addresses is much lower than that for data (*e.g.* a burst requires a single address but maybe four or eight data transfers). Availability of independently scalable resources might, for example, lead to medium complexity designs sharing a single internal address channel while providing multiple data read and write channels.

Finally, some of the key incremental features of the AXI protocol can be listed as follows:

- support for out-of-order completion of transactions

- easy addition of register stages to provide timing closure

- support for multiple address issuing

- separate read and write data channels to enable low-cost Direct Memory Access (DMA)

- support for unaligned data transfers

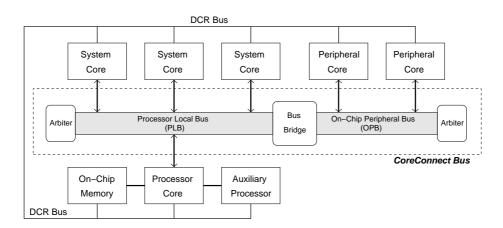

## 2.3 CoreConnect Bus

CoreConnect is an IBM-developed on-chip bus that eases the integration and reuse of processor, sub-system and peripheral cores within standard product platform designs. It is a complete and versatile architecture clearly targeting high performance systems, and many of its features might be overkill in simple embedded applications [13].

The CoreConnect bus architecture serves as the foundation of IBM Blue Logic<sup>TM</sup>or other non-IBM devices. The Blue Logic ASIC/SOC design methodology is the approach proposed by IBM [6] to extend conventional ASIC design flows to current design needs: low-power and multiple-voltage products, reconfigurable logic, custom design capability, and analog/mixed-signal designs. Each of these offerings requires a well-balanced coupling of technology capabilities and design methodology. The use of this bus architecture allows the hierarchical design of SoCs.

As can be seen in figure 2.4, the IBM CoreConnect architecture provides three buses for interconnecting cores, library macros, and custom logic:

- Processor Local Bus (PLB).

- On-Chip Peripheral Bus (OPB).

- Device Control Register (DCR) Bus.

The PLB bus connects the processor to high-performance peripherals, such as memories, DMA controllers, and fast devices. Bridged to the PLB, the OPB supports slower-speed peripherals. Finally, the DCR bus is a separate control bus that connects all devices, controllers, and bridges and provides a separate

Figure 2.4: Schematic structure of the CoreConnect bus.

path to set and monitor the individual control registers. It is designed to transfer data between the CPU's general purpose registers and the slave logic's device control registers. It removes configuration registers from the memory address map, which reduces loading and improves bandwidth of the PLB.

This architecture shares many high-performance features with the AMBA Bus specification. Both architectures allow split, pipelined and burst transfers, multiple bus masters and 32, 64 or 128-bits architectures. On the other hand, CoreConnect also supports multiple masters in the peripheral bus.

Please note that design toolkits are available for the CoreConnect bus and include functional models, monitors, and a bus functional language to drive the models. These toolkits provide an advanced validation environment for engineers designing macros to attach to the PLB, OPB and DCR buses.

### 2.3.1 Processor Local Bus (PLB)

The PLB is the main system bus targeting high performance and low latency on-chip communication. More specifically, PLB is a synchronous, multi-master, arbitrated bus. It supports *concurrent read and write transfers*, thus yielding a maximum bus utilization of two data transfers per clock cycle. Moreover, PLB implements *address pipelining*, that reduces bus latency by overlapping a new write request with an ongoing write transfer and up to three read requests with an ongoing read transfer [14].

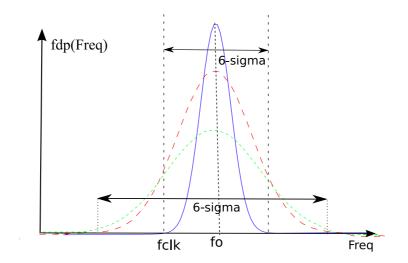

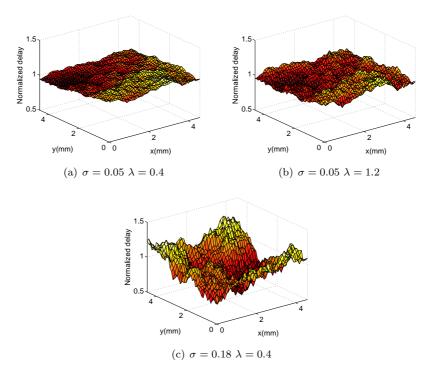

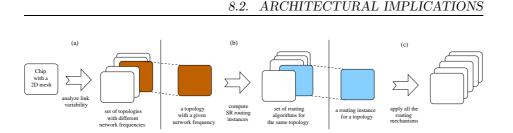

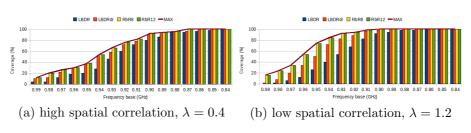

Access to PLB is granted through a central arbitration mechanism that allows masters to compete for bus ownership. This arbitration mechanism is flexible enough to provide for the implementation of various *priority schemes*. In fact, four levels of request priority for each master allow PLB implementation with various arbitration priority schemes. Additionally, an arbitration locking mechanism is provided to support master-driven atomic operations. PLB also exhibits the ability to overlap the bus request/grant protocol with an ongoing transfer.